Sfr definition 19.2. smod1: uart1 mode, Sfr definition 19.2 – Silicon Laboratories C8051F347 User Manual

Page 219

Rev. 1.3

219

C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D

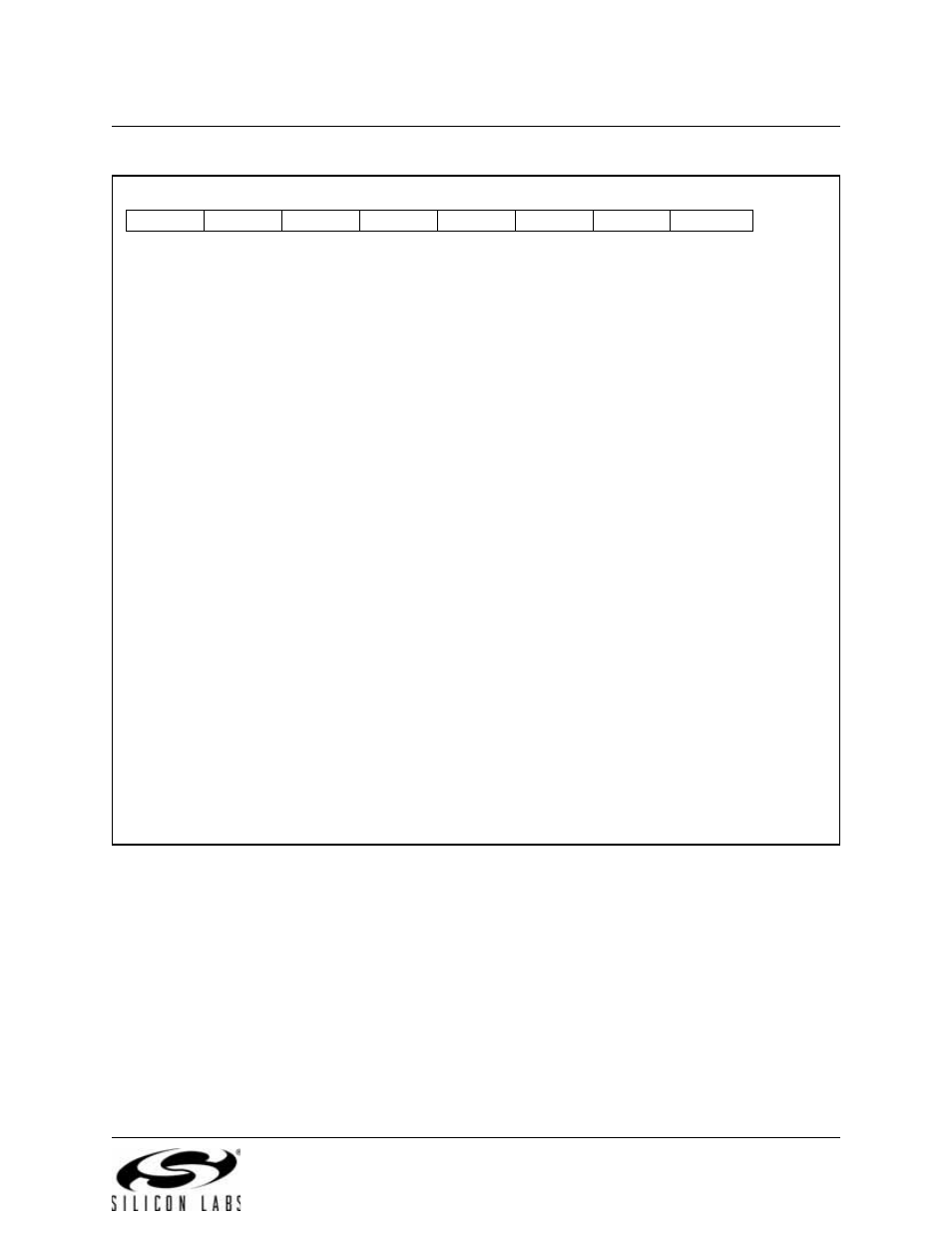

SFR Definition 19.2. SMOD1: UART1 Mode

Bit7:

MCE1: Multiprocessor Communication Enable.

0: RI will be activated if stop bit(s) are ‘1’.

1: RI will be activated if stop bit(s) and extra bit are ‘1’ (extra bit must be enabled using

XBE1).

Note: This function is not available when hardware parity is enabled.

Bits6–5: S1PT[1:0]: Parity Type.

00: Odd

01: Even

10: Mark

11: Space

Bit4:

PE1: Parity Enable.

This bit activates hardware parity generation and checking. The parity type is selected by

bits S1PT1-0 when parity is enabled.

0: Hardware parity is disabled.

1: Hardware parity is enabled.

Bits3–2: S1DL[1:0]: Data Length.

00: 5-bit data

01: 6-bit data

10: 7-bit data

11: 8-bit data

Bit1:

XBE1: Extra Bit Enable

When enabled, the value of TBX1 will be appended to the data field.

0: Extra Bit Disabled.

1: Extra Bit Enabled.

Bit0:

SBL1: Stop Bit Length

0: Short - Stop bit is active for one bit time.

1: Long - Stop bit is active for two bit times (data length = 6, 7, or 8 bits), or 1.5 bit times

(data length = 5 bits).

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Reset Value

MCE1

S1PT1

S1PT0

PE1

S1DL1

S1DL0

XBE1

SBL1

00001100

Bit7

Bit6

Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

SFR Address:

0xE5