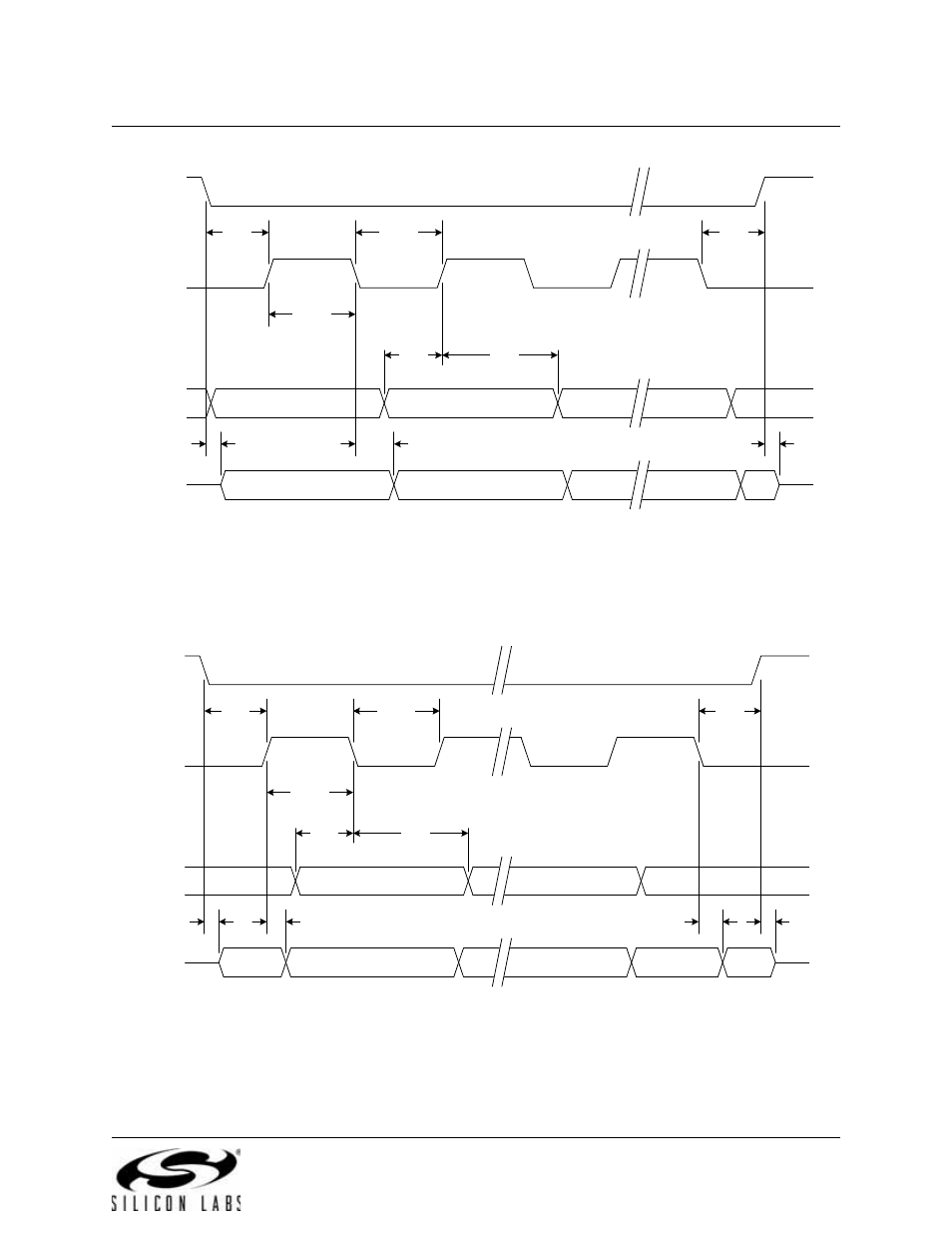

Figure 20.10. spi slave timing (ckpha = 0), Figure 20.11. spi slave timing (ckpha = 1) – Silicon Laboratories C8051F347 User Manual

Page 233

Rev. 1.3

233

C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D

Figure 20.10. SPI Slave Timing (CKPHA = 0)

Figure 20.11. SPI Slave Timing (CKPHA = 1)

SCK*

T

SE

NSS

T

CKH

T

CKL

MOSI

T

SIS

T

SIH

MISO

T

SD

T

SOH

* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

T

SEZ

T

SDZ

SCK*

T

SE

NSS

T

CKH

T

CKL

MOSI

T

SIS

T

SIH

MISO

T

SD

T

SOH

* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

T

SLH

T

SEZ

T

SDZ