Silicon Laboratories C8051F347 User Manual

Page 85

Rev. 1.3

85

C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D

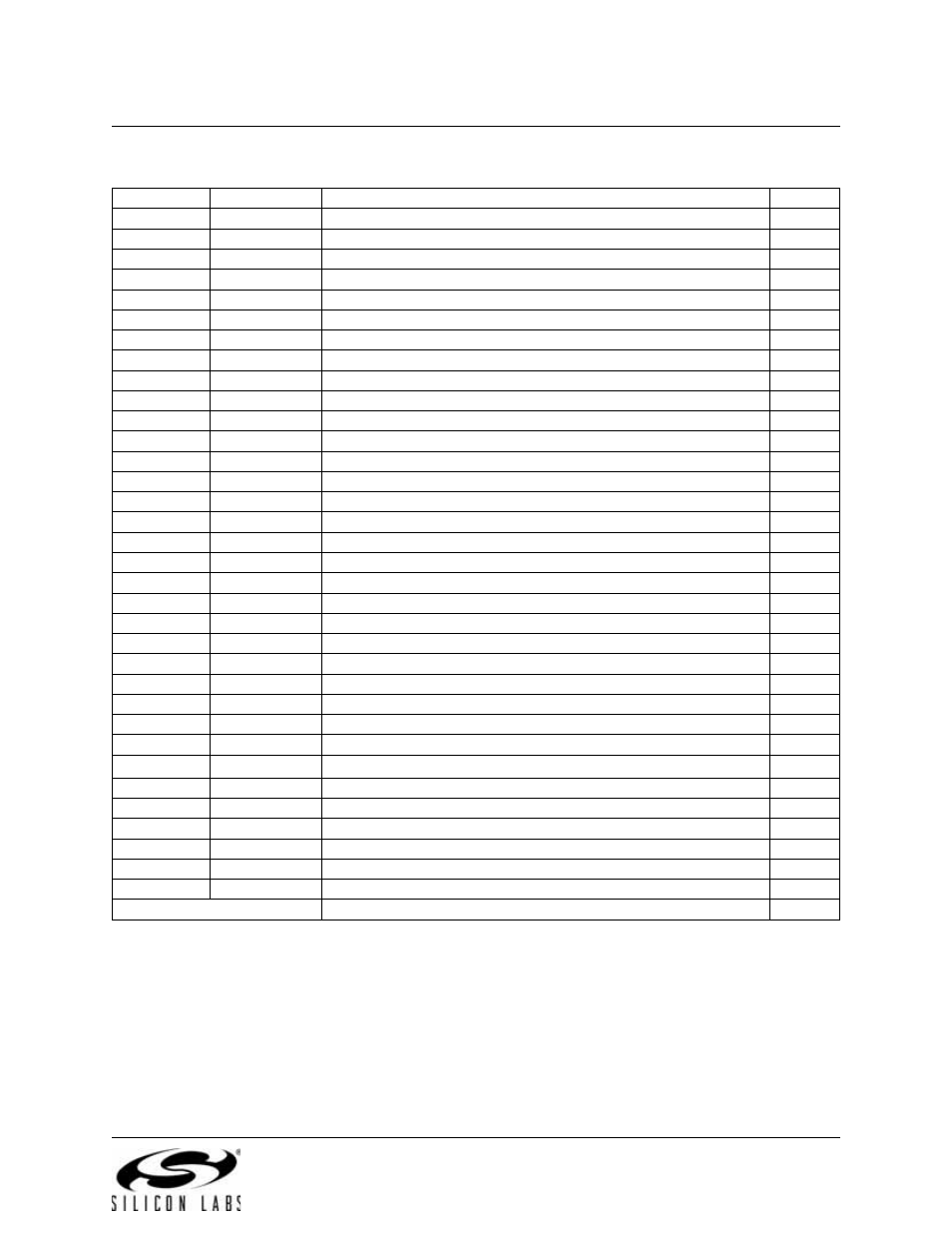

SBUF0

0x99

UART0 Data Buffer

SCON0

0x98

UART0 Control

SMB0CF

0xC1

SMBus Configuration

SMB0CN

0xC0

SMBus Control

SMB0DAT

0xC2

SMBus Data

SMOD1

0xE5

UART1 Mode

SP

0x81

Stack Pointer

SPI0CFG

0xA1

SPI Configuration

SPI0CKR

0xA2

SPI Clock Rate Control

SPI0CN

0xF8

SPI Control

SPI0DAT

0xA3

SPI Data

TCON

0x88

Timer/Counter Control

TH0

0x8C

Timer/Counter 0 High

TH1

0x8D

Timer/Counter 1 High

TL0

0x8A

Timer/Counter 0 Low

TL1

0x8B

Timer/Counter 1 Low

TMOD

0x89

Timer/Counter Mode

TMR2CN

0xC8

Timer/Counter 2 Control

TMR2H

0xCD

Timer/Counter 2 High

TMR2L

0xCC

Timer/Counter 2 Low

TMR2RLH

0xCB

Timer/Counter 2 Reload High

TMR2RLL

0xCA

Timer/Counter 2 Reload Low

TMR3CN

0x91

Timer/Counter 3Control

TMR3H

0x95

Timer/Counter 3 High

TMR3L

0x94

Timer/Counter 3Low

TMR3RLH

0x93

Timer/Counter 3 Reload High

TMR3RLL

0x92

Timer/Counter 3 Reload Low

VDM0CN

0xFF

V

DD

Monitor Control

USB0ADR

0x96

USB0 Indirect Address Register

USB0DAT

0x97

USB0 Data Register

USB0XCN

0xD7

USB0 Transceiver Control

XBR0

0xE1

Port I/O Crossbar Control 0

XBR1

0xE2

Port I/O Crossbar Control 1

XBR2

0xE3

Port I/O Crossbar Control 2

All Other Addresses

Reserved

Table 9.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

Register

Address

Description

Page