Sfr definition 5.3. adc0cf: adc0 configuration, Sfr definition 5.4. adc0h: adc0 data word msb, Sfr definition 5.5. adc0l: adc0 data word lsb – Silicon Laboratories C8051F347 User Manual

Page 50: Ad0sc sysclk clk

C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D

50

Rev. 1.3

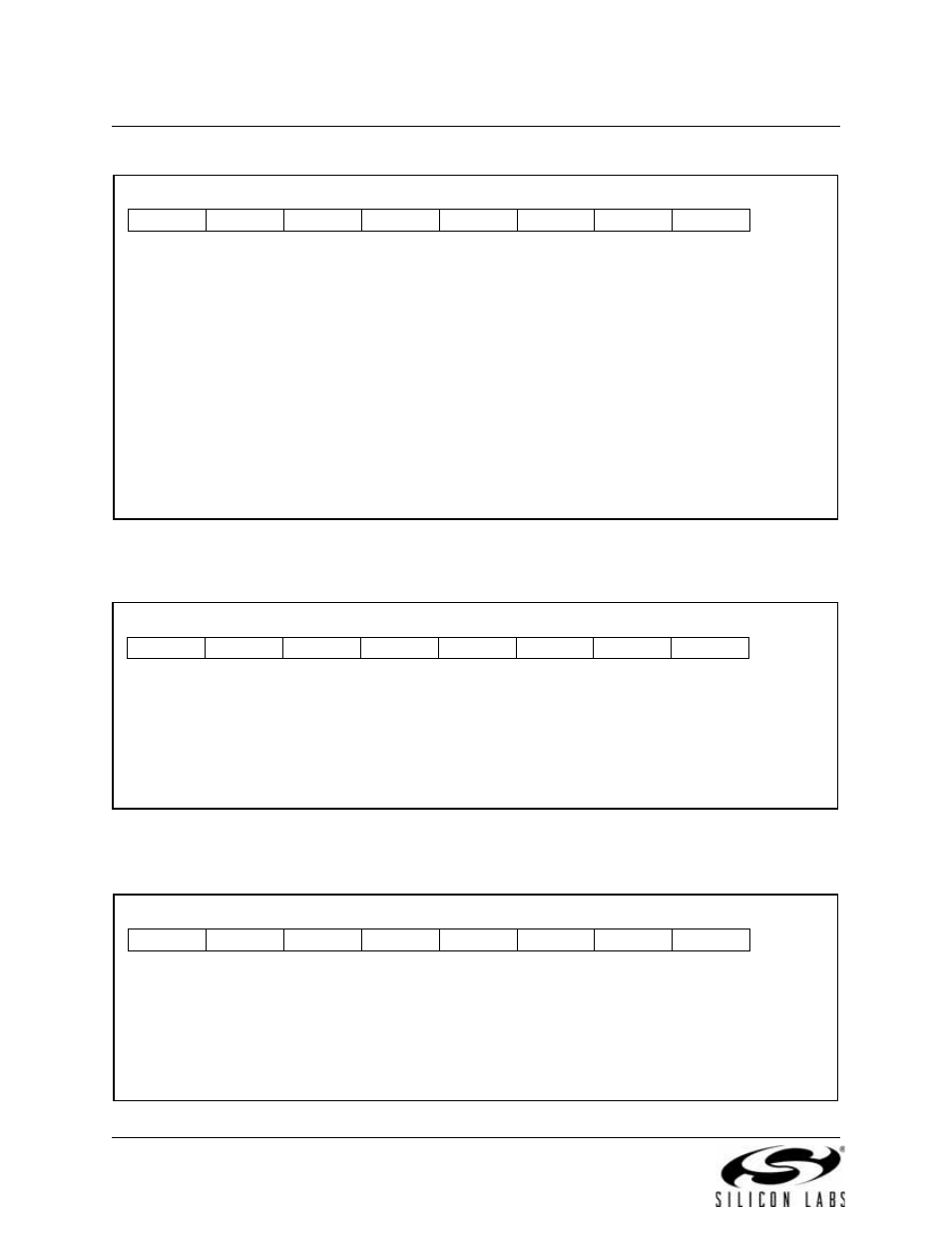

SFR Definition 5.3. ADC0CF: ADC0 Configuration

SFR Definition 5.4. ADC0H: ADC0 Data Word MSB

SFR Definition 5.5. ADC0L: ADC0 Data Word LSB

Bits7–3: AD0SC4–0: ADC0 SAR Conversion Clock Period Bits.

SAR Conversion clock is derived from system clock by the following equation, where

AD0SC refers to the 5-bit value held in bits AD0SC4-0. SAR Conversion clock requirements

are given in Table 5.1.

Bit2:

AD0LJST: ADC0 Left Justify Select.

0: Data in ADC0H:ADC0L registers are right-justified.

1: Data in ADC0H:ADC0L registers are left-justified.

Bits1–0: UNUSED. Read = 00b; Write = don’t care.

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Reset Value

AD0SC4

AD0SC3

AD0SC2

AD0SC1

AD0SC0

AD0LJST

-

-

11111000

Bit7

Bit6

Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

SFR Address:

0xBC

AD0SC

SYSCLK

CLK

SAR

----------------------

1

–

=

Bits7–0: ADC0 Data Word High-Order Bits.

For AD0LJST = 0: Bits 7–2 are the sign extension of Bit1. Bits 1-0 are the upper 2 bits of the

10-bit ADC0 Data Word.

For AD0LJST = 1: Bits 7–0 are the most-significant bits of the 10-bit ADC0 Data Word.

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Reset Value

00000000

Bit7

Bit6

Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

SFR Address:

0xBE

Bits7–0: ADC0 Data Word Low-Order Bits.

For AD0LJST = 0: Bits 7–0 are the lower 8 bits of the 10-bit Data Word.

For AD0LJST = 1: Bits 7–6 are the lower 2 bits of the 10-bit Data Word. Bits 5–0 will always

read ‘0’.

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Reset Value

00000000

Bit7

Bit6

Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

SFR Address:

0xBD