Figure 1.3. c8051f348/c block diagram, Rev. 1.3 21 – Silicon Laboratories C8051F347 User Manual

Page 21

Rev. 1.3

21

C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D

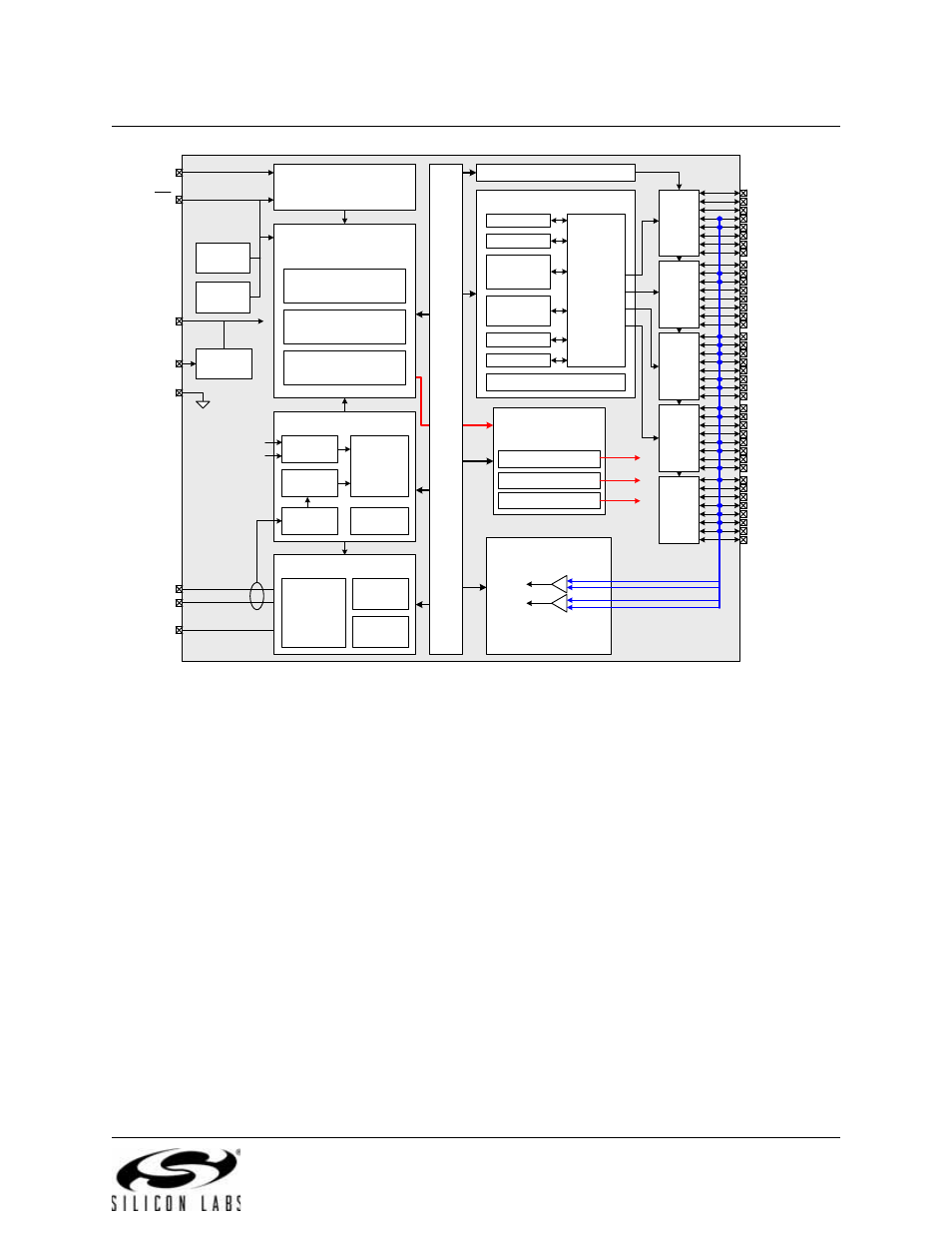

Figure 1.3. C8051F348/C Block Diagram

Debug / Programming

Hardware

Port 0

Drivers

P0.0

Port I/O Configuration

Digital Peripherals

Priority

Crossbar

Decoder

Crossbar Control

Power-On

Reset

Power

Net

UART0

Timers 0, 1,

2, 3

PCA/WDT

SMBus

UART1

SPI

P0.1

P0.2

P0.3

P0.4

P0.5

P0.6/XTAL1

P0.7/XTAL2

Port 1

Drivers

Port 2

Drivers

Port 3

Drivers

Port 4

Drivers

P1.0

P1.1

P1.2

P1.3

P1.4/CNVSTR

P1.5/VREF

P1.6

P1.7

P2.0

P2.1

P2.2

P2.3

P2.4

P2.5

P2.6

P2.7

P3.0

P3.1

P3.2

P3.3

P3.4

P3.5

P3.6

P3.7

P4.0

P4.1

P4.2

P4.3

P4.4

P4.5

P4.6

P4.7

Supply

Monitor

System Clock Setup

External

Oscillator

Internal

Oscillator

XTAL1

XTAL2

Low Freq.

Oscillator

Clock

Multiplier

Clock

Recovery

USB Peripheral

Controller

1k Byte

RAM

Full / Low

Speed

Transceiver

External Memory

Interface

Control

Address

Data

P1

P2 / P3

P4

Voltage

Regulator

D+

D-

VBUS

VDD

VREG

GND

C2CK/RST

Reset

C2D

CIP-51 8051

Controller Core

64/32 kB ISP FLASH

Program Memory

256 Byte RAM

4/2 kB XRAM

Analog Peripherals

2 Comparators

+

-

CP0

+

-

CP1

SFR

Bus