Internal h-f oscillator suspend mode – Silicon Laboratories C8051F347 User Manual

Page 132

C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D

132

Rev. 1.3

14.1. Programmable Internal High-Frequency (H-F) Oscillator

All C8051F34x devices include a programmable internal oscillator that defaults as the system clock after a

system reset. The internal oscillator period can be programmed via the OSCICL register shown in SFR

Definition 14.2. The OSCICL register is factory calibrated to obtain a 12 MHz internal oscillator frequency.

Electrical specifications for the precision internal oscillator are given in Table 14.1 on page 141. Note that

the system clock may be derived from the programmed internal oscillator divided by 1, 2, 4, or 8, as

defined by the IFCN bits in register OSCICN. The divide value defaults to 8 following a reset.

14.1.1. Internal H-F Oscillator Suspend Mode

The internal high-frequency oscillator may be placed in Suspend mode by writing ‘1’ to the SUSPEND bit in

register OSCICN. In Suspend mode, the internal H-F oscillator is stopped until a non-idle USB event is

detected (

) or VBUS matches the polarity selected by the VBPOL bit in register REG0CN (

). Note that the USB transceiver can still detect USB events when it is disabled.

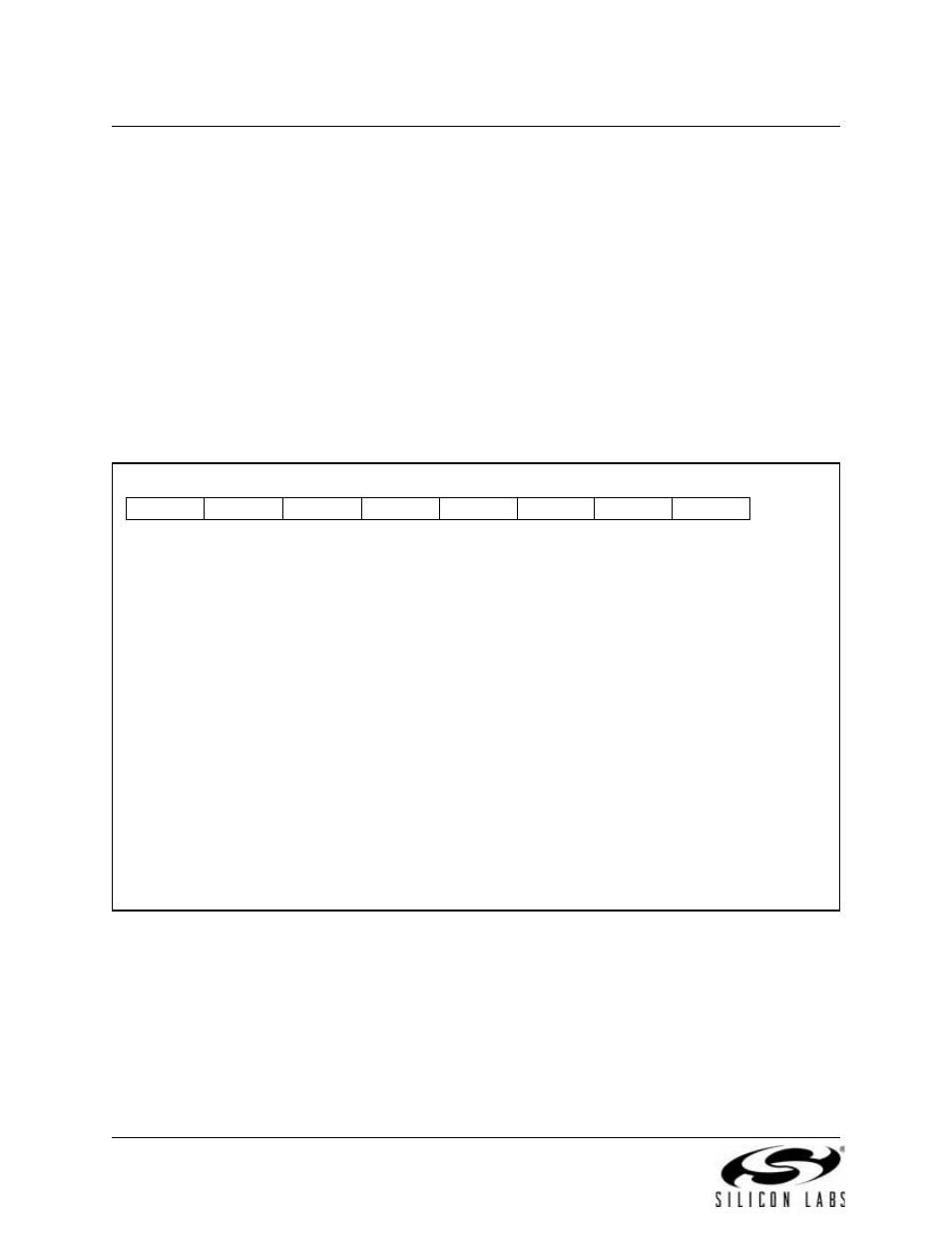

SFR Definition 14.1. OSCICN: Internal H-F Oscillator Control

Bit7:

IOSCEN: Internal H-F Oscillator Enable Bit.

0: Internal H-F Oscillator Disabled.

1: Internal H-F Oscillator Enabled.

Bit6:

IFRDY: Internal H-F Oscillator Frequency Ready Flag.

0: Internal H-F Oscillator is not running at programmed frequency.

1: Internal H-F Oscillator is running at programmed frequency.

Bit5:

SUSPEND: Force Suspend

Writing a ‘1’ to this bit will force the internal H-F oscillator to be stopped. The oscillator will be

re-started on the next non-idle USB event (i.e., RESUME signaling) or VBUS interrupt event

(see SFR Definition 8.1).

Bits4–2: UNUSED. Read = 000b, Write = don't care.

Bits1–0: IFCN1–0: Internal H-F Oscillator Frequency Control.

00: SYSCLK derived from Internal H-F Oscillator divided by 8.

01: SYSCLK derived from Internal H-F Oscillator divided by 4.

10: SYSCLK derived from Internal H-F Oscillator divided by 2.

11: SYSCLK derived from Internal H-F Oscillator divided by 1.

R/W

R

R/W

R

R/W

R/W

R/W

R/W

Reset Value

IOSCEN

IFRDY

SUSPEND

-

-

-

IFCN1

IFCN0

10000000

Bit7

Bit6

Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

SFR Address:

0xB2