Sfr definition 21.4. tl0: timer 0 low byte, Sfr definition 21.5. tl1: timer 1 low byte, Sfr definition 21.6. th0: timer 0 high byte – Silicon Laboratories C8051F347 User Manual

Page 242: Sfr definition 21.7. th1: timer 1 high byte

C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D

242

Rev. 1.3

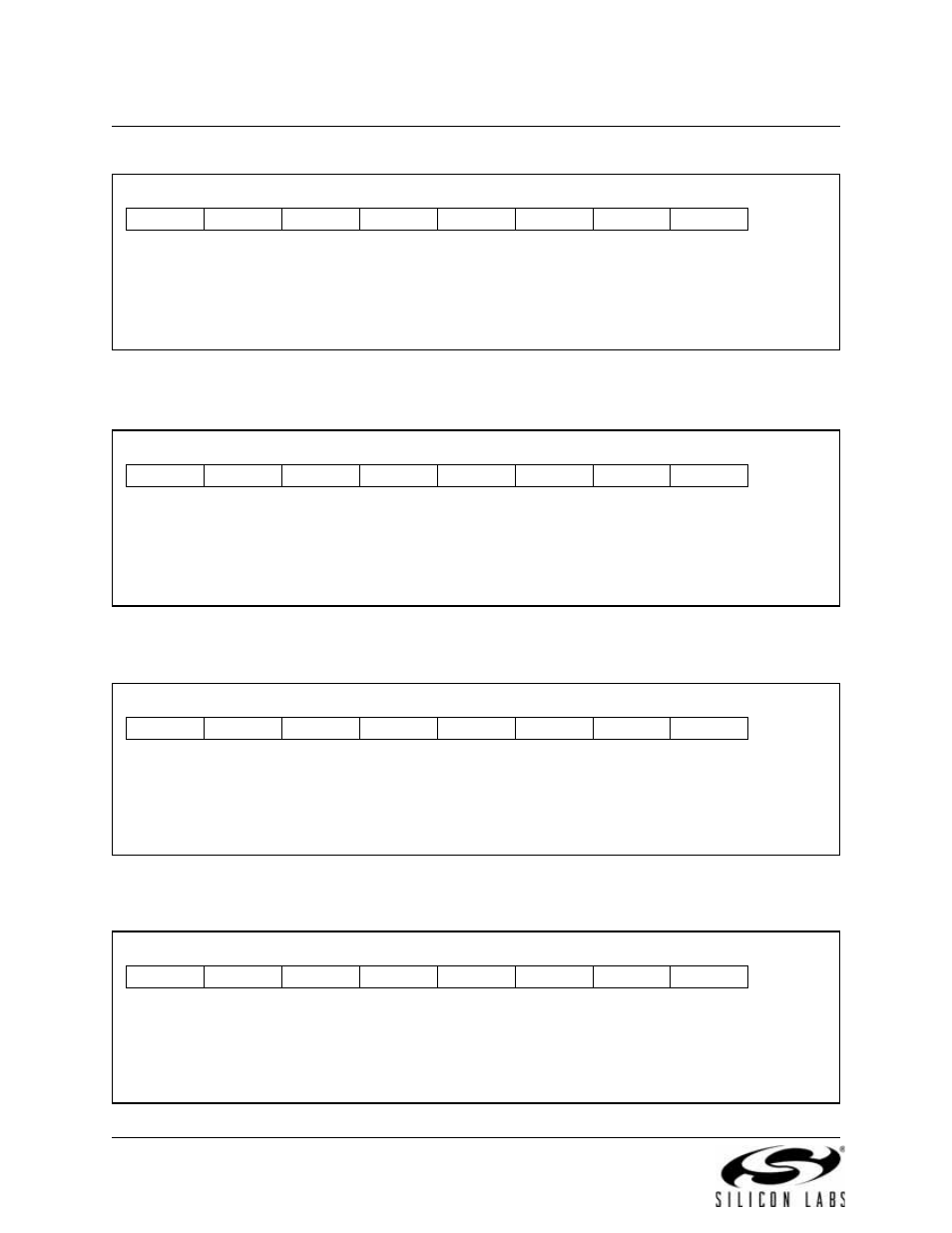

SFR Definition 21.4. TL0: Timer 0 Low Byte

SFR Definition 21.5. TL1: Timer 1 Low Byte

SFR Definition 21.6. TH0: Timer 0 High Byte

SFR Definition 21.7. TH1: Timer 1 High Byte

Bits 7–0: TL0: Timer 0 Low Byte.

The TL0 register is the low byte of the 16-bit Timer 0.

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Reset Value

00000000

Bit7

Bit6

Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

SFR Address:

0x8A

Bits 7–0: TL1: Timer 1 Low Byte.

The TL1 register is the low byte of the 16-bit Timer 1.

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Reset Value

00000000

Bit7

Bit6

Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

SFR Address:

0x8B

Bits 7–0: TH0: Timer 0 High Byte.

The TH0 register is the high byte of the 16-bit Timer 0.

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Reset Value

00000000

Bit7

Bit6

Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

SFR Address:

0x8C

Bits 7–0: TH1: Timer 1 High Byte.

The TH1 register is the high byte of the 16-bit Timer 1.

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Reset Value

00000000

Bit7

Bit6

Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

SFR Address:

0x8D