Movx instruction and program memory, Table 9.1. cip-51 instruction set summary – Silicon Laboratories C8051F347 User Manual

Page 75

Rev. 1.3

75

C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D

9.1.2. MOVX Instruction and Program Memory

In the CIP-51, the MOVX instruction serves three purposes: accessing on-chip XRAM, accessing off-chip

data XRAM (only on C8051F340/1/4/5/8 devices), and accessing on-chip program Flash memory. The

Flash access feature provides a mechanism for user software to update program code and use the pro-

gram memory space for non-volatile data storage (see

Section “12. Flash Memory” on page 107

). The

External Memory Interface (only on C8051F340/1/4/5/8 devices) provides a fast access interface to

off-chip data XRAM (or memory-mapped peripherals) via the MOVX instruction. Refer to Section

“

13. External Data Memory Interface and On-Chip XRAM

. for details.

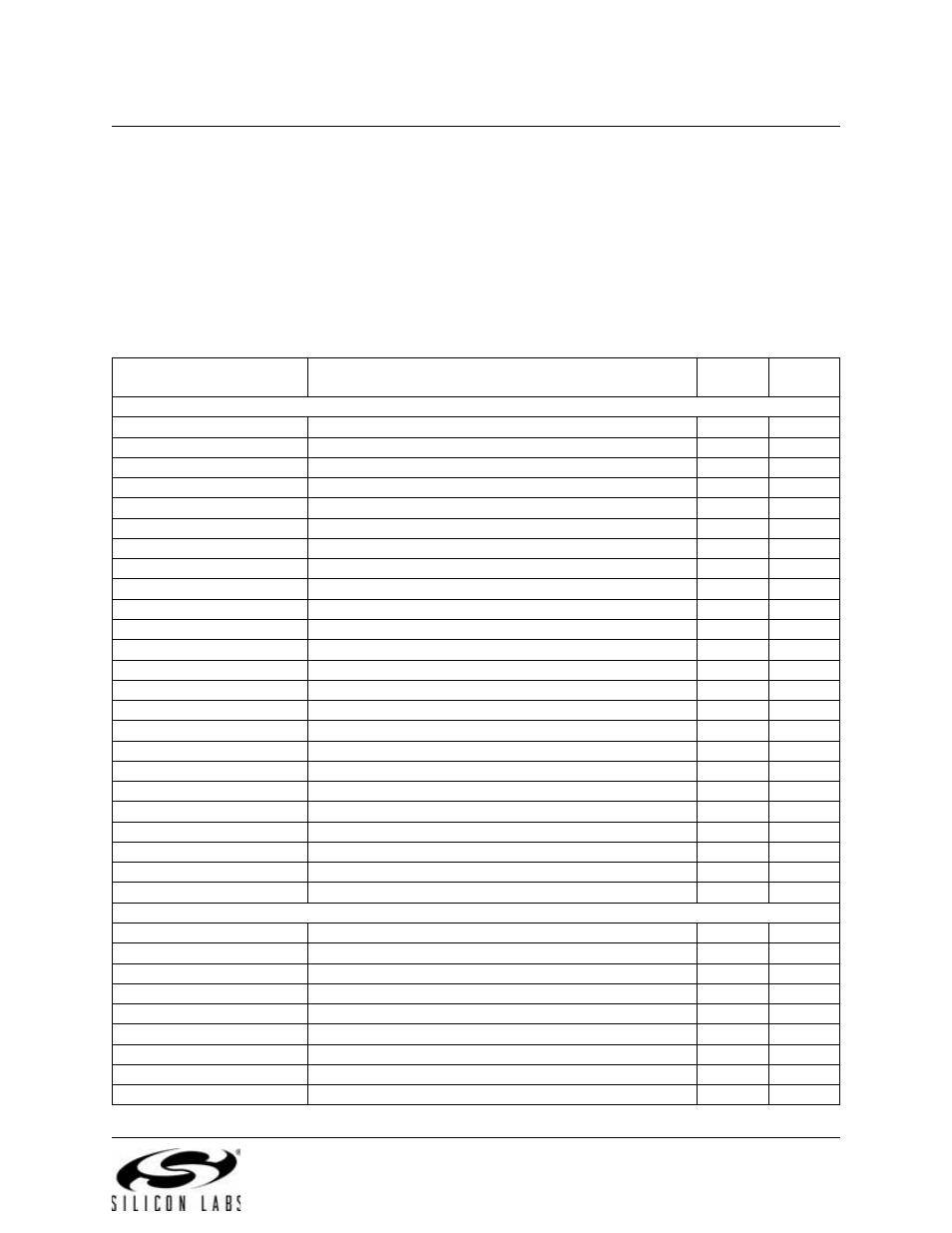

Table 9.1. CIP-51 Instruction Set Summary

Mnemonic

Description

Bytes

Clock

Cycles

Arithmetic Operations

ADD A, Rn

Add register to A

1

1

ADD A, direct

Add direct byte to A

2

2

ADD A, @Ri

Add indirect RAM to A

1

2

ADD A, #data

Add immediate to A

2

2

ADDC A, Rn

Add register to A with carry

1

1

ADDC A, direct

Add direct byte to A with carry

2

2

ADDC A, @Ri

Add indirect RAM to A with carry

1

2

ADDC A, #data

Add immediate to A with carry

2

2

SUBB A, Rn

Subtract register from A with borrow

1

1

SUBB A, direct

Subtract direct byte from A with borrow

2

2

SUBB A, @Ri

Subtract indirect RAM from A with borrow

1

2

SUBB A, #data

Subtract immediate from A with borrow

2

2

INC A

Increment A

1

1

INC Rn

Increment register

1

1

INC direct

Increment direct byte

2

2

INC @Ri

Increment indirect RAM

1

2

DEC A

Decrement A

1

1

DEC Rn

Decrement register

1

1

DEC direct

Decrement direct byte

2

2

DEC @Ri

Decrement indirect RAM

1

2

INC DPTR

Increment Data Pointer

1

1

MUL AB

Multiply A and B

1

4

DIV AB

Divide A by B

1

8

DA A

Decimal adjust A

1

1

Logical Operations

ANL A, Rn

AND Register to A

1

1

ANL A, direct

AND direct byte to A

2

2

ANL A, @Ri

AND indirect RAM to A

1

2

ANL A, #data

AND immediate to A

2

2

ANL direct, A

AND A to direct byte

2

2

ANL direct, #data

AND immediate to direct byte

3

3

ORL A, Rn

OR Register to A

1

1

ORL A, direct

OR direct byte to A

2

2

ORL A, @Ri

OR indirect RAM to A

1

2