Figure 91. reset source (rstsrc) register, Chapter 9 minimum hardware considerations, 1 identifying the reset source – Intel 8XC196Lx User Manual

Page 91: Chapter 9, Minimum hardware considerations, Identifying the reset source -1, Reset source (rstsrc) register -1, Chapter 9 — minimum hardware considerations

9-1

CHAPTER 9

MINIMUM HARDWARE CONSIDERATIONS

This chapter discusses the major hardware consideration differences between the 8XC196Lx and

the 8XC196Kx. The 8XC196Lx has implemented a reset source SFR that reveals the source of

the most recent reset request.

9.1

IDENTIFYING THE RESET SOURCE

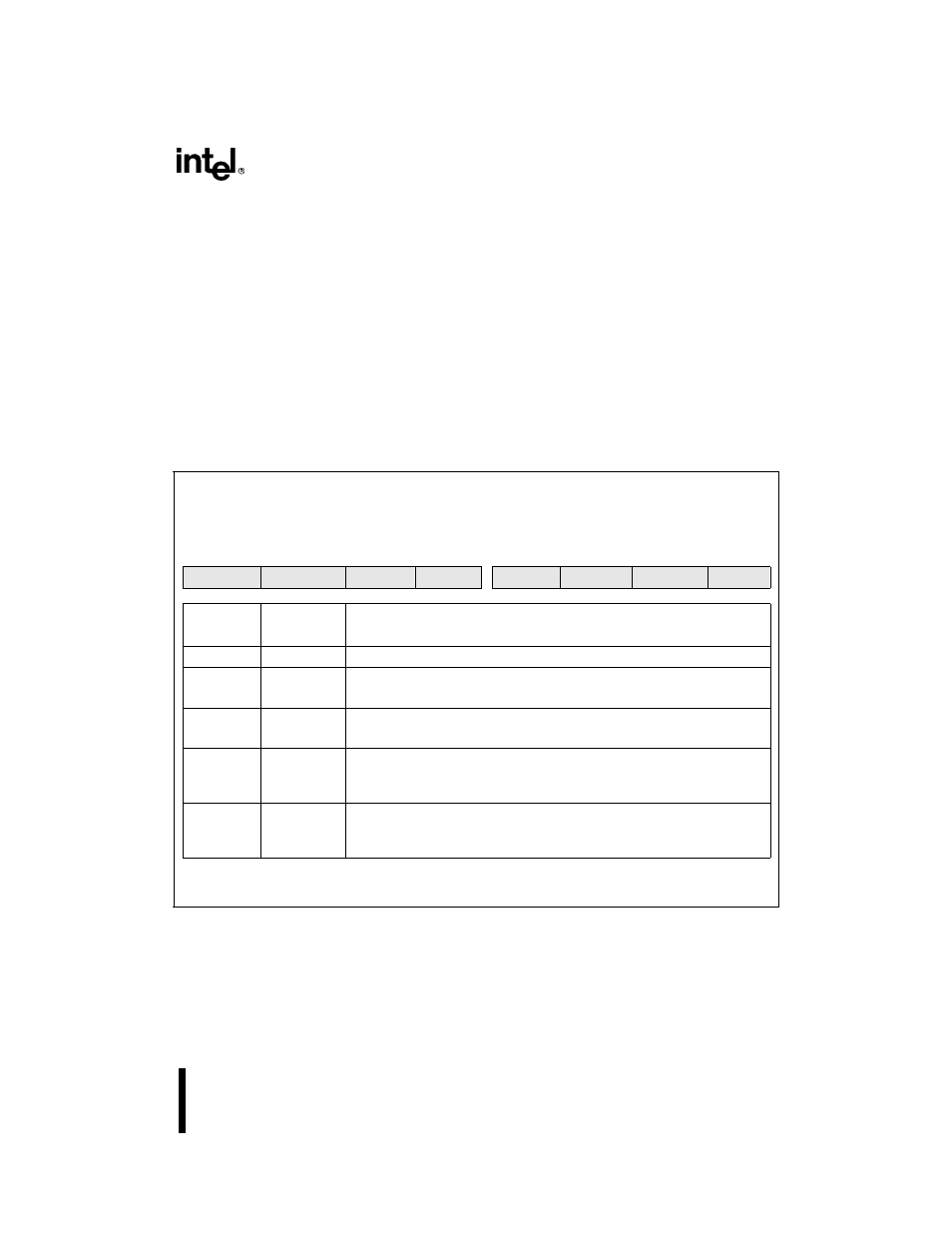

The reset source (RSTSRC) register indicates the source of the last reset that the microcontroller

encountered (Figure 9-1). If more than one reset occurs at the same time, all of the corresponding

RSTSRC bits are set. Reading this SFR clears all the register bits.

RSTSRC

Address:

Reset State:

1F92H

XXH

(1)

The reset source (RSTSRC) register indicates the source(s) of the last reset that the microcontroller

encountered.

7

0

—

—

—

—

CFDRST

WDTRST

SFWRST

EXTRST

Bit

Number

Bit

Mnemonic

Function

7:4

—

Reserved; for compatibility with future devices, write zeros to these bits.

3

CFDRST

Clock Failure Detection Reset

When set, this bit indicates that a failed clock caused the last reset.

2

WDTRST

Watchdog Timer Reset

When set, this bit indicates that the watchdog timer caused the last reset.

1

SFWRST

Software Reset

When set, this bit indicates that either the RST instruction or the IDLPD

instruction used with an illegal key caused the last reset.

0

EXTRST

External Reset

When set, this bit indicates that the RESET# pin being asserted caused the

last reset.

NOTE:

1.

The State of the RSTSRC register is inderterminate on a V

CC

power up condition. All other reset

states will have the corresponding reset event bit set in the register.

Figure 9-1. Reset Source (RSTSRC) Register