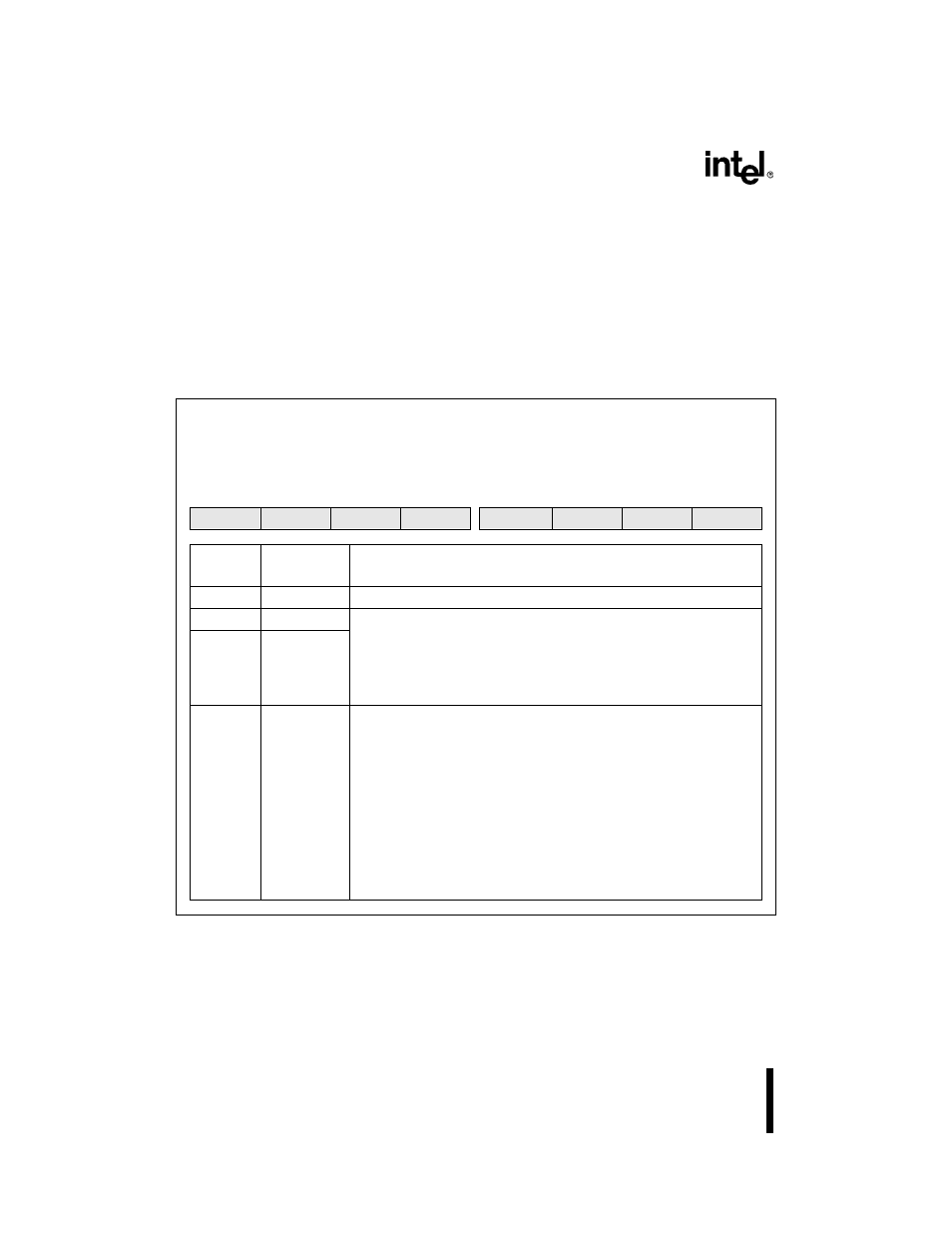

Figure 62. ssio 1 clock (ssio1_clk) register (con, 2 ssio 1 clock register, Ssio 1 clock register -2 – Intel 8XC196Lx User Manual

Page 54: Ssio 1 clock (ssio1_clk) register -2

8XC196L

X SUPPLEMENT

6-2

For transmissions, SSIO0_CLK determines whether the SSIO shifts out data bits on rising or fall-

ing clock edges. For receptions, SSIO0_CLK determines whether the SSIO samples data bits on

rising or falling clock edges.

6.2

SSIO 1 CLOCK REGISTER

SSIO1_CLK selects the SSIO mode of operation (standard, duplex, or channel-select), enables

the channel-select master contention interrupt request, and selects the phase and polarity for the

serial clock (SC1) for channels. In standard mode, use this register to configure the serial clock

for channel 1.

SSIO1_CLK

Address:

Reset State:

1FB7H

00H

The SSIO 1 clock (SSIO1_CLK) register selects the SSIO mode of operation (standard, duplex, or

channel-select), enables the channel-select master contention interrupt request, and selects the

phase and polarity for the serial clock (SC1) for channel 1.

7

0

—

—

CHS

DUP

CONINT

CONPND

PHAS

POLS

Bit

Number

Bit

Mnemonic

Function

7:6

—

Reserved; for compatibility with future devices, write zeros to these bits.

5

CHS

These bits determine the SSIO operating mode.

CHS DUP

0

0

standard mode

0

1

duplex mode

1

0

channel-select half-duplex mode (uses SD1 only)

1

1

channel-select full-duplex mode (uses both SD0 and SD1)

4

DUP

3

CONINT

Master Contention Interrupt

For channel-select master operations, the SSIO sets the master

contention interrupt pending bit (CONPND) when the CHS# pin is

externally activated. In a system with multiple masters, an external

master activates the CHS# signal to request control of the serial clock.

CONINT determines whether the SSIO sets both CONPND and the

SSIO0 interrupt pending bit or only CONPND when the CHS# pin is

externally activated.

0 = SSIO sets only CONPND

1 = SSIO sets both CONPND and the SSIO0 interrupt pending bit

This bit is valid for channel-select master operations and ignored for all

other operations.

Figure 6-2. SSIO 1 Clock (SSIO1_CLK) Register