Table 81. j1850 controller signals, Table 82. control and status registers (continued, 2 j1850 controller signals and registers – Intel 8XC196Lx User Manual

Page 69: J1850 controller signals and registers -3, J1850 controller signals -3, Control and status registers -3

8-3

J1850 COMMUNICATIONS CONTROLLER

8.2

J1850 CONTROLLER SIGNALS AND REGISTERS

Table 8-1 describes the J1850 controller’s pins, and Table 8-2 describes the control and status

registers.

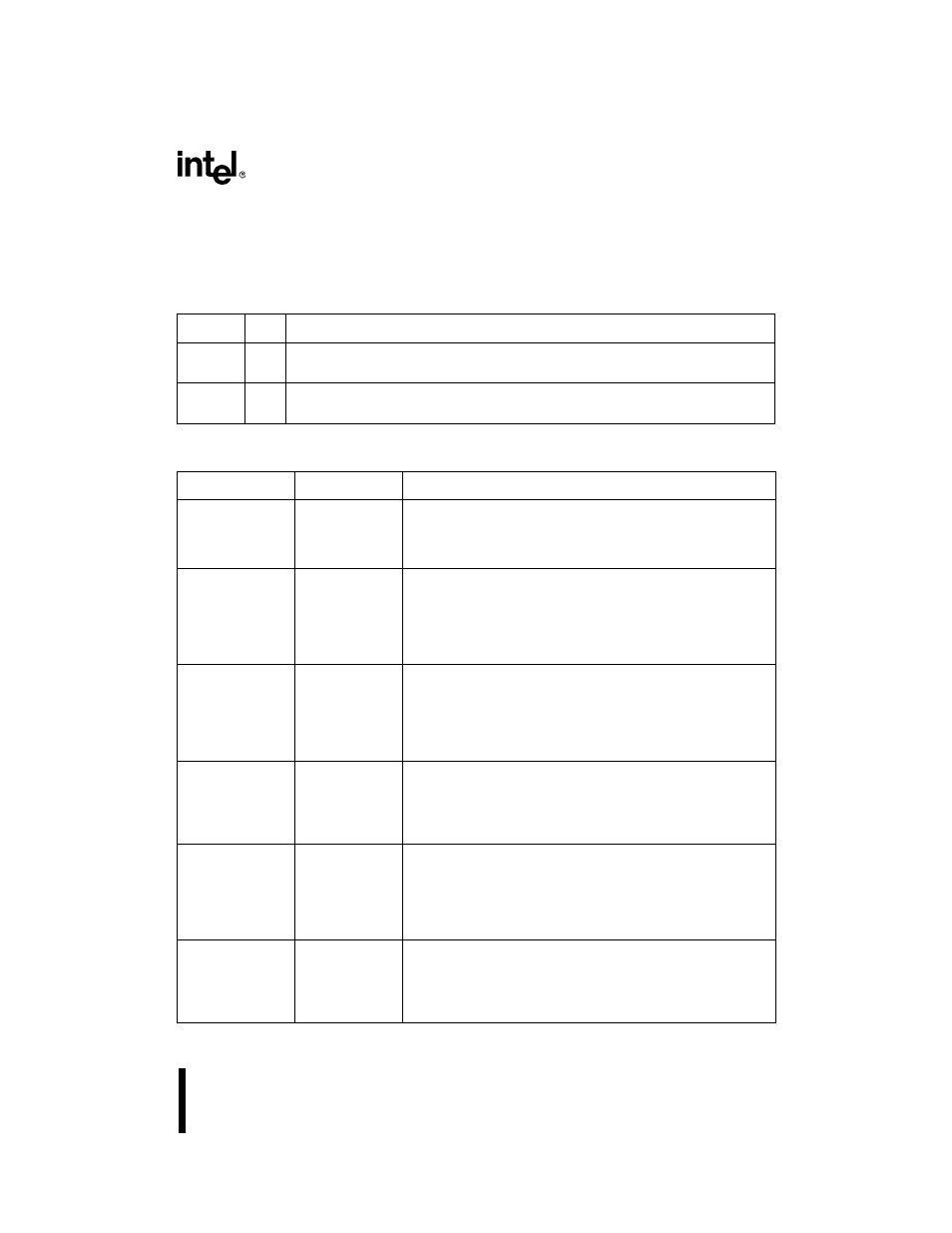

Table 8-1. J1850 Controller Signals

Signal

Type

Description

RXJ1850

I

Receive

Carries digital symbols from a remote transceiver to the J1850 controller.

TXJ1850

O

Transmit

Carries digital symbols from the J1850 controller to a remote transceiver.

Table 8-2. Control and Status Registers

Mnemonic

Address

Description

J_CFG

1F54H

J1850 Configuration

Program this byte register to specify the oscillator prescaler

divisor, mode of operation, and normalization bit format. You must

write to this register during the initialization sequence.

J_CMD

1F51H

J1850 Command

Program this byte register to specify the number of bytes to be

transmitted in the next message frame. This register also

monitors the status of the message transmission in progress, and

it can abort, ignore, or retry a message if necessary. Read this

register to determine the status of transmissions in progress.

J_DLY

1F58H

J1850 Delay Compensation

Program this byte register to define the length of the delay time

through the external transceiver to compensate for the inherent

propagation delays and to accurately resolve bus contention

during arbitration. You must write to this register during the

initialization sequence.

J_RX

1F52H

J1850 Receiver

Read this byte register to receive data in byte increments from the

J1850 bus to the microcontroller CPU. This register is buffered to

allow for reception of a second data byte while the first data byte

is being read.

J_STAT

1F53H

J1850 Status

Read this byte register to determine the current status of the

receive and transmit buffers and the J1850 interrupt sources. You

can also determine bus status and in-frame response messaging

status. All bits of this register are cleared when read, with the

exception of the BUS_STAT bit.

J_TX

1F50H

J1850 Transmitter

Program this byte register to transmit data in byte increments to

the J1850 bus from the microcontroller CPU. This register is

buffered to allow for writing of a second data byte while the first

data byte is being shifted out.