Table 51. microcontroller ports, Chapter 5 i/o ports, 1 i/o ports overview – Intel 8XC196Lx User Manual

Page 45: 2 internal structure for ports 1, 2, 5, and 6 (b, Chapter 5, I/o ports, I/o ports overview -1, Microcontroller ports -1, Chapter 5 — i/o ports

5-1

CHAPTER 5

I/O PORTS

The I/O ports of the 8XC196Lx are functionally identical to those of the 8XC196Jx. However, on

the 87C196LA and LB, the reset state level of all 41 general-purpose I/O pins has changed from

a weak logic “1” (wk1) to a weak logic “0” (wk0). This chapter outlines the differences between

the 87C196LA, LB and the 8XC196Kx controllers.

5.1

I/O PORTS OVERVIEW

Table 5-1 provides an overview of the 8XC196Lx and 8XC196Kx I/O ports.

5.2

INTERNAL STRUCTURE FOR PORTS 1, 2, 5, AND 6 (BIDIRECTIONAL

PORTS)

Figure 5-1 shows the logic for driving the output transistors, Q1 and Q2. Consult the datasheet

for specifications on the amount of current that each port can source or sink.

In I/O mode (selected by clearing a port mode register bit), the port data output and the port di-

rection registers are input to the multiplexers. These signals combine to drive the gates of Q1 and

Q2 so that the output is high, low, or high impedance.

In special-function mode (selected by setting a port mode register bit), SFDIR and SFDATA are

input to the multiplexers. These signals combine to drive the gates of Q1 and Q2 so that the output

is high, low, or high impedance. Special-function output signals clear SFDIR; special-function

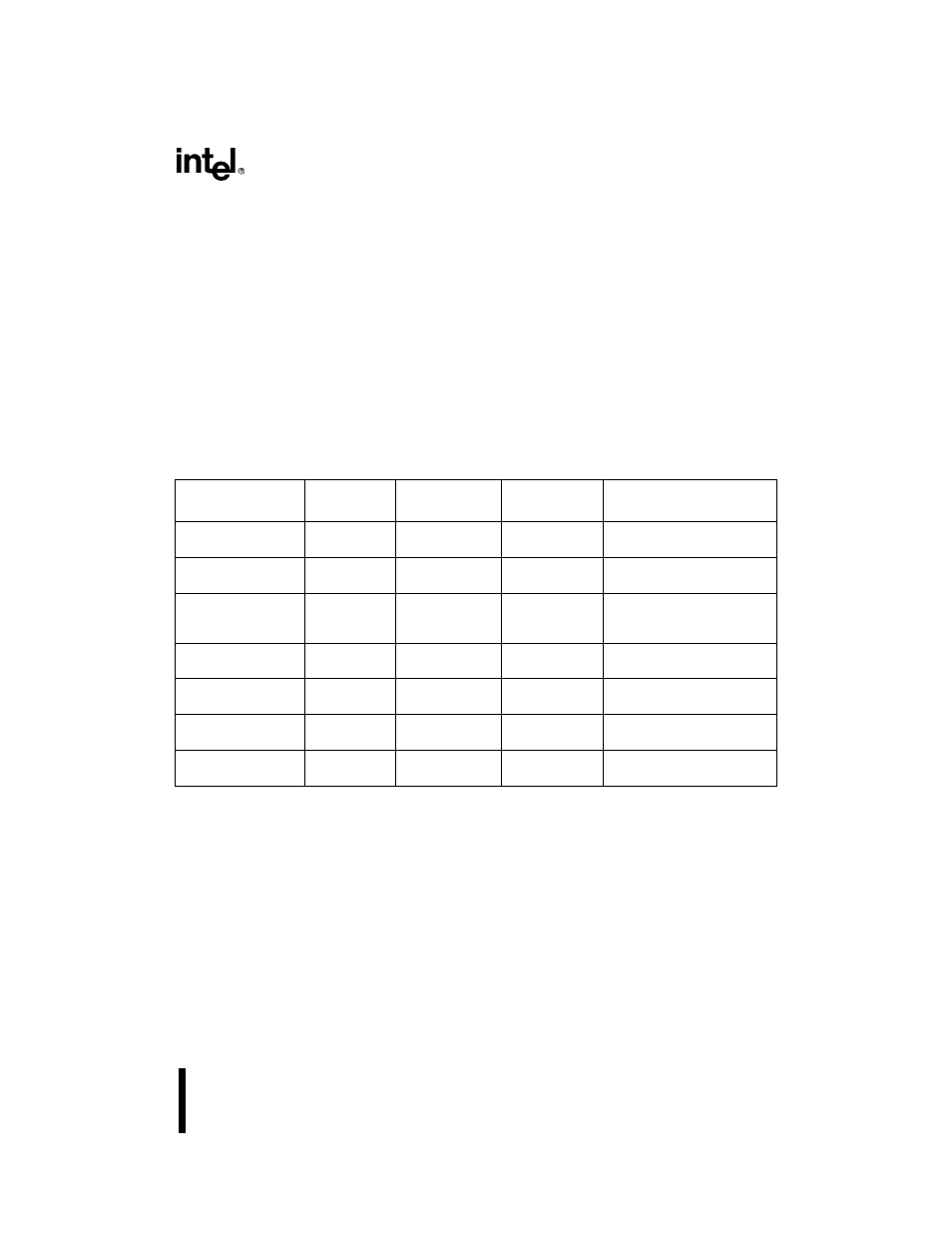

Table 5-1. Microcontroller Ports

Port

Pins

Type

Configuration

Options

Associated Peripheral or

System Function

Port 0

8 (K

x)

6 (CA, J

x, Lx)

Standard

Input-only

A/D converter

(not supported on LD)

Port 1

8 (K

x)

4 (CA, J

x, Lx)

Standard

Complementary

Open-drain

EPA and timers

Port 2

8 (K

x)

6 (CA, J

x, Lx)

Standard

Complementary

Open-drain

J1850 (LB only), SIO,

interrupts, bus control, clock

gen.

Port 3

8

Memory mapped

Complementary

Open-drain

Address/data bus

Port 4

8

Memory mapped

Complementary

Open-drain

Address/data bus

Port 5

8 (K

x)

3 (CA, J

x, Lx)

Memory mapped

Complementary

Open-drain

Bus control, slave port

Port 6

8 (K

x)

6 (CA, J

x, Lx)

Standard

Complementary

Open-drain

EPA, SSIO