Table 21. features of the 8xc196lx and 8xc196kx p, Chapter 2 architectural overview, 1 microcontroller features – Intel 8XC196Lx User Manual

Page 15: Chapter 2, Architectural overview, Microcontroller features -1, Features of the 8xc196l

2-1

CHAPTER 2

ARCHITECTURAL OVERVIEW

This chapter describes architectural differences between the 8XC196Lx (87C196LA, 87C196LB,

and 83C196LD) and the 8XC196Kx (8XC196Kx, 8XC196Jx, and 87C196CA) microcontroller

families. Both the 8XC196Lx and the 8XC196Kx are designed for high-speed calculations and

fast I/O, and share a common architecture and instruction set with few deviations. This chapter

provides a high-level overview of the deviations between the two families.

NOTE

This supplement describes two product families within the MCS

®

96

microcontroller family. For brevity, the name 8XC196Lx is used when the

discussion applies to all three Lx controllers. Likewise, the name 8XC196Kx is

used when the discussion applies to all the Kx, Jx, and CA controllers.

2.1

MICROCONTROLLER FEATURES

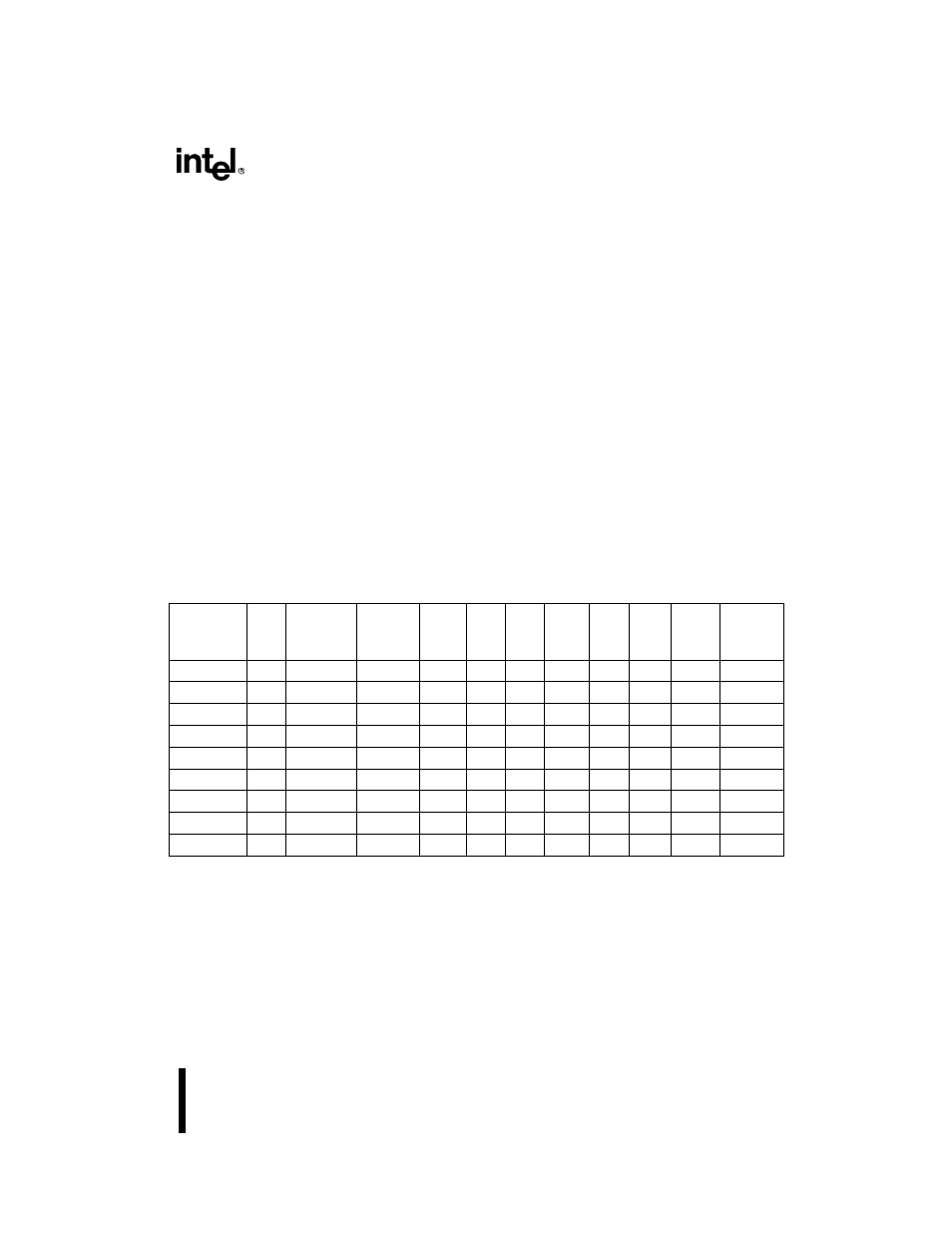

Table 2-1 lists the features of the 8XC196Lx and the 8XC196Kx.

Table 2-1. Features of the 8XC196L

x and 8XC196Kx Product Famiies

Device

Pins

OTPROM/

EPROM/

ROM (1)

Register

RAM (2)

Code

RAM

I/O

Pins

EPA

Pins

SIO/

SSIO

Ports

A/D

CAN

J1850

Ext.

Interrupt

Pins

87C196LA

52

24 K

768

—

41

6

3

6

—

—

1

87C196LB

52

24 K

768

—

41

6

3

6

—

1

1

83C196LD

52

16 K

384

—

41

6

3

—

—

—

1

8XC196JV

52

48 K

1536

512

41

6

3

6

—

—

1

8XC196KT

68

32 K

1024

512

56

10

3

8

—

—

2

8XC196JT

52

32 K

1024

512

41

6

3

6

—

—

1

87C196CA

68

32 K

1024

256

51

6

3

6

1

—

2

8XC196KR

68

16 K

512

256

56

10

3

8

—

—

2

8XC196JR

52

16 K

512

256

41

6

3

6

—

—

1

NOTES:

1.

Optional. The second character of the device name indicates the presence and type of nonvolatile

memory. 80C196

xx = none; 83C196xx = ROM; 87C196xx = OTPROM or EPROM.

2.

Register RAM amounts include the 24 bytes allocated to core SFRs and the stack pointer.