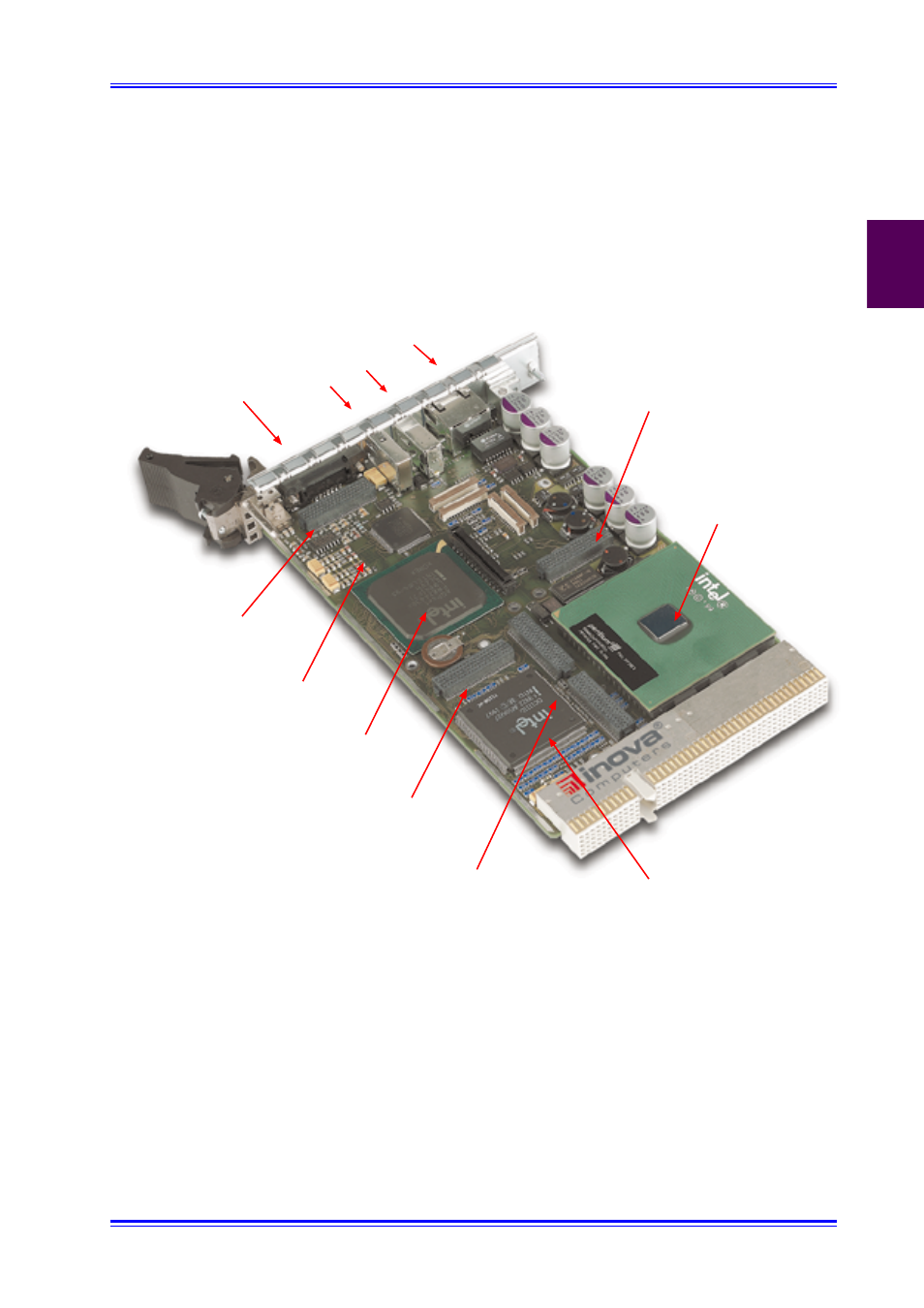

Figure 1.20 icp-piii overview, Figure 1.20 icp-piii overview -7, Compactpci – Inova High Performance CPU board ICP-PII User Manual

Page 17: Product overview, Icp-piii

©2002 Inova Computers GmbH

Page 1-7

Doc. PD00581013.004

ICP-PIII

Product Overview

CompactPCI

®

1

100/10Mbit

Ethernet

FLASH Extension:

Up to 512MByte

TFT,

GigaST

Ȣ

R,

PanelLink or LVDS

North-Bridge

Optional

Multiprocessing

Socket 370 or

BGA2 based

Intel Pentium III

or Celeron

Inova’s CPUs have been prepared for rear I/O operation. Currently (RIO-C), EIDE, FireWire2, USB2,

LPT1 and the loudspeaker signals are present on the backplane (if requested at time of order.)

Other options may also be available (including customer specific) but are not referred to in this

user’s handbook. In order to take full advantage of the rear I/O features, the CompactPCI back-

plane needs to support them. Inova provides two standard versions; one has the J2 connector at

the CPU location extended to the rear of the backplane while the other version has all slots fitted

with the J2 connector on both the front and rear.

Figure 1.20 ICP-PIII Overview

VGA,

GigaST

Ȣ

R

PanelLink

LVDS,

FireWire

USB

Optional Lynx3DM or

Radeon VE Graphic

C o n t r o l l e r ( U n d e r -

side)

128MB or 384MB

SDRAM Extension

512MByte in Development

PCI Interface for

Piggyback Extensions