2 configuration, Table 1.20 ‘processor overview, 2 configuration -6 – Inova High Performance CPU board ICP-PII User Manual

Page 16: Table 1.20 ‘processor overview -6, Product overview, Icp-piii 1.2 configuration

©2002 Inova Computers GmbH

Page 1-6

Doc. PD00581013.004

Product Overview

ICP-PIII

1.2 Configuration

Inova’s high-performance, high-density 3U PIII board supports functionality and connectivity on

all three major serial networking levels like Fast Ethernet, FireWire and USB as well as most state-of-

the-art fieldbus standards such as PROFIBUS, CAN, Interbus, and LON.

Three CPU groups exist to cater for the needs of all aspects of CompactPCI integration: The high-

end typically supports 128MBytes on-board soldered SDRAM, Lynx3DM graphic controller with

8MByte SGRAM and all I/O. For standard applications, the same base layout is utilized however,

the soldered SDRAM, graphic controller and many of the peripheral connections are absent for

use in typical embedded applications. Finally, for multiprocessing applications, the PCI/PCI trans-

parent bridge is replaced by the 21554 non-transparent version.

All CPU family members can possess up to 512MByte SDRAM with BIOS controlled ECC through

a combination of soldered memory units and plug-in modules. FLASH up to 512MByte may be

realised in a similar manner. All CPUs are equipped with a shielded front-panel with typically VGA,

USB, FireWire and Fast Ethernet interfaces installed. Other front-panels are available with mouse,

keyboard, COM, LPT, TFT, PanelLink or dual Ethernet interfaces. The choice of Lynx 3DM or ATI

Radeon VE graphic controller complete with 8/16MByte video RAM is available as an option as is

multiprocessing.

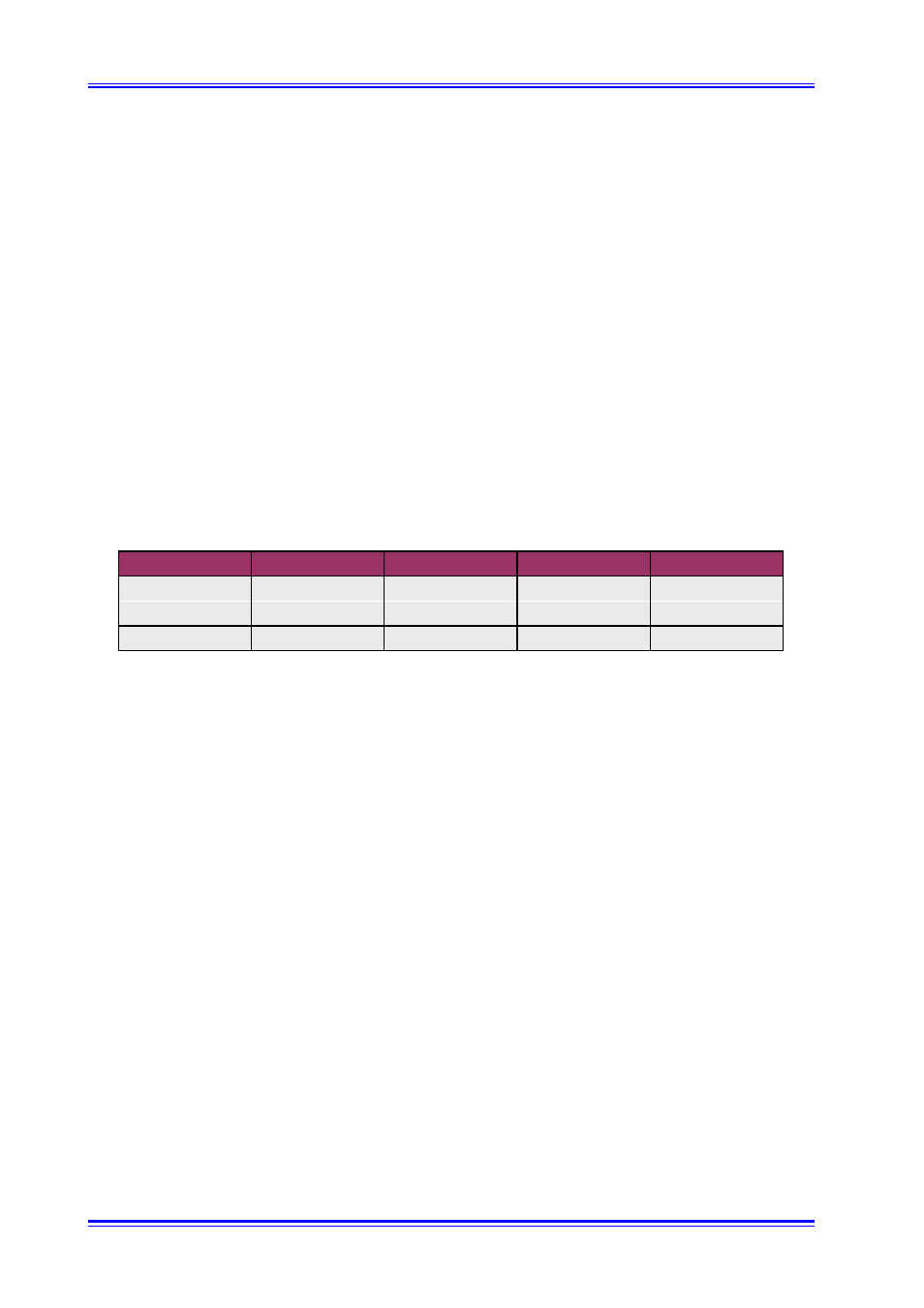

Table 1.20 ‘Processor Overview

CPU Family

Processor

CPU Speed(s)

Multi-Processing

Package

ICP-PIII-fegsm

Intel PIII

400 to 850MHz

No

FC-PGA

ICP-SPIII-fegsm

Intel PIII

400 to 850MHz

Yes

FC-PGA

ICP-xxPIII-fegsm

Mobile PIII/Celeron

400 to 700MHz

Yes / No

BGA2 (Interposer)