Eiki LC-X71 LC-X71L User Manual

Page 54

- 54 -

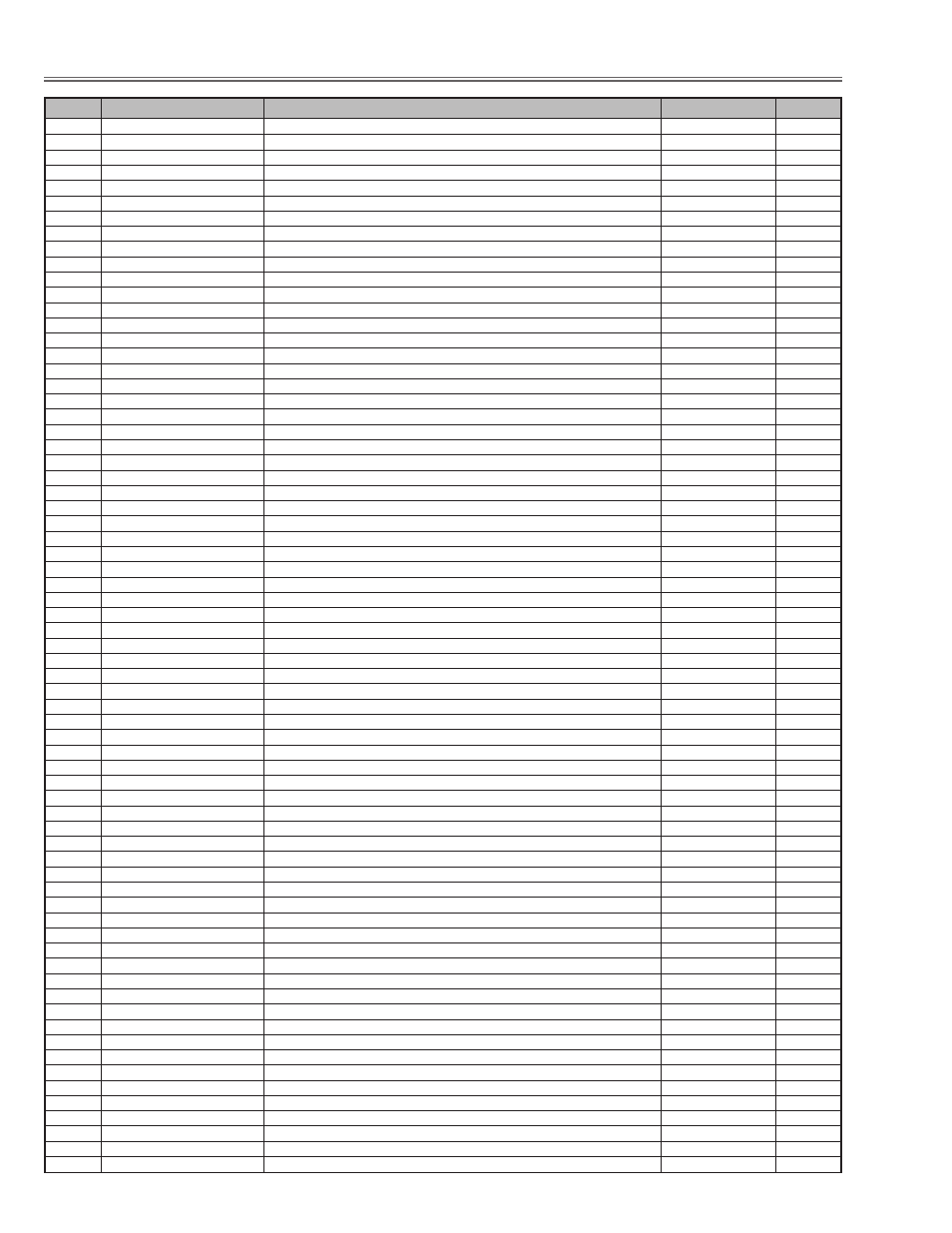

137 GND

Power

(0V)

-

-

138

PW_RESET

Reset for PW

Reset with L>H>L

O

139 1.9V

Power

(1.9V)

-

-

140

PW_SEL

PIXEL 232C Selection

SH:H, PW:L

O

141

EXP_RESET

I/O Expander Reset Signal

Reset: H

O

142

RESET_GAM

Reset for Digital Gamma IC

O

143

TDO [for ICE]

Test Data output

-

O

144 (Not

used)

(Open)

O

145 (Not

used)

(Open)

O

146

SH_FPG_WAIT

Hardware Wait Request

Wait with L

I

147

RESETM

Manual Reset Request

-

I

148

(Reserved)

Analog Trigger/Inout Port H

(Open)

I

149 (Not

used)

(Pull-down)

I

150

ASEMD0 [for ICE]

ASE Mode

-

I

151

ASEBRKAK [for ICE]

ASE Brake

-

O

152 (Not

used)

(Pull-up)

I

153

AUDATA[3] [for ICE]

AUD data

-

O

154

AUDATA[2] [for ICE]

AUD data

-

O

155 GND

Power

(0V)

-

-

156

AUDATA[1] [for ICE]

AUD data

-

O

157 1.9V

Power

(1.9V)

-

-

158

AUDATA[0] [for ICE]

AUD data

-

O

159 GND

Power

for

Inout/Output(0V)

-

-

160

TRST [for ICE]

Test Reset

-

I

161 3.3V

Power

for

Inout/Output(3.3V)

-

-

162

TMS [for ICE]

Test Mode Switch

-

I

163

TDI [for ICE]

Test Data Input

-

I

164

TCK [for ICE]

test Clock

-

I

165 (Not

used)

(Pull-down)

I

166 (Not

used)

(Pull-down)

I

167

LAMP_DET

Lamp Fail Detection I Lamp Failure Detection until Dimmer Starts

L: Lamp fail

I

168 SWF_INIT

Config.

status

signal

I

169

MD0

Clock Mode Setting [Default:L]

L fixed

I

170

1.9V

PLL1 Power (1.9V)

-

-

171

CAP1

PLL1 External Condenser - [470pF]

-

-

172

GND

PLL1 Power (0V)

-

-

173

GND

PLL2 Power (0V)

-

-

174

CAP2

PLL2 External Condenser - [470pF]

-

-

175

1.9V

PLL2 Power (1.9V)

-

-

176

AUDCK [for ICE]

AUD Clock

-

I

177 GND

Power

(0V)

-

-

178 1.9V

Power

(1.9V)

-

-

179 (Reserved)

Clock

Oscillator

(Open)

-

180 EXTAL

External

Click/X'TAL

-

I

181

SWF_DONE

Config. process finishing signal

I

182

BOX_SW

Detect on/Off for PJ-Net Board

L: Yes, H: No

I

183

FPGA_nSTATUS

Error Detection during the Config.

H:Error

I

184

FPGA_CONF_DONE

OK Detection during the Config.

H:OK

I

185

SH_FLASH_WP

Flash IC Write Protect

L: Protect

O

186 PFC_SW_EX

PFC_SW

O

187 SWF_D0

Config.

data

O

188 GND

Power

for

Inout/Output(0V)

-

-

189 CKIO

System

Clock

IO

-

I/O

190 3.3V

Power

for

Inout/Output(3.3V)

-

-

191

SH_LB_UART

Dimmer Control

H: at lamp ON

O

192 (Not

used)

(Open)

-

193 (Not

used)

(Open)

-

194 (Not

used)

(Pull-up)

-

195

SH_EX_UART

Send Data2 [External]

19200 or 9600bps

O

196 (Not

used)

(Pull-up)

-

197 (Not

used)

(Pull-up)

-

198

LB_SH_UART

Dimmer control and lamp error detect

-

I

199 (Not

used)

(Pull-up)

-

200 GND

Power

(0V)

-

-

201

EX_SH_UART

Receive Data2 [External]

19200 or 9600bps

I

202 1.9V

Power

(1.9V)

-

-

203 (Not

used)

(Pull-up)

I

204

FPGA_NCONFIG

Start config.

L -> H start

O

205

NET_H/L

Request command for PJNet

Active L

O

Pin No.

Function Name

Function

Polarity

I/O

Control Port Functions