6 control interface pins, Control interface pins, Chip control signal description – Avago Technologies LSI53C120 User Manual

Page 37: Scsi control signal description, Power and ground signal description

Signal Descriptions

3-7

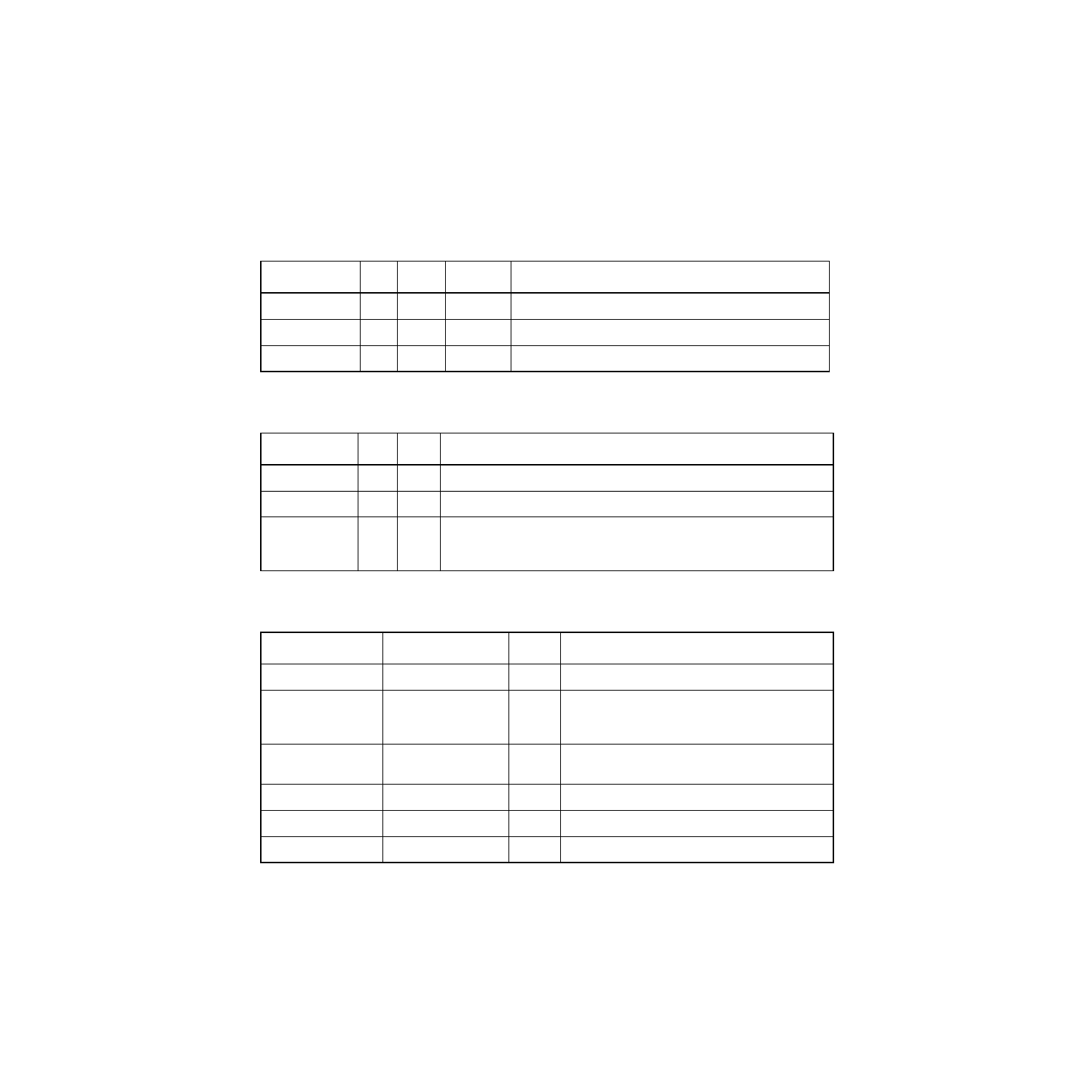

3.1.6 Control Interface Pins

Tables

through

list the various control interface pins.

Table 3.4

Chip Control Signal Description

Control

Pin

Type

Strength

Description

RESET/

44

I

Master reset, active low.

WS_ENABLE/

38

I

Enable/disable SCSI transfers through the LSI53C120.

XFER_ACTIVE

126

O

16 mA

Transfers through the LSI53C120 are enabled/disabled.

Table 3.5

SCSI Control Signal Description

SCSI Control

Pin

Type

Description

CLOCK

47

I

40 MHz input clock

DIFF_MODE/

48

I

SCSI B-side bus mode control

DIFF_SENSE

49

I

The DIFF_SENSE pin detects the presence of a single-ended device

on a differential system. This pin should be tied low during single-

ended operation and pulled high during differential operation.

Table 3.6

Power and Ground Signal Description

Power and Ground Pin

Type

Description

VDD-SCSI

3, 37, 66, 100

I/O

Power supplies to the SCSI bus I/O pins

VSS-SCSI

7, 12, 17, 22, 28, 33,

70, 75, 81, 86, 91,

96

I/O

Power supplies to the SCSI bus I/O pins

VSS_IO

41, 53, 63, 105, 115,

127

I/O

Power supplies to the I/O pins

VDD_IO

45, 58, 110, 122

I/O

Power supplies to the I/O pins

VDD_CORE

46, 121

CORE

Power supplies to the CORE logic

VSS_CORE

50, 116

CORE

Power supplies to the CORE logic