9 control signals, Control signals, Diff_sense control signal polarity – Avago Technologies LSI53C120 User Manual

Page 28: Reset/ control signal polarity

2-10

Functional Description

shows the DIFF_SENSE control signal polarity to illustrate its

possible signal levels, states and subsequent effects.

2.2.9 Control Signals

This section provides information about the RESET/, WS_ENABLE/, and

XFER_ACTIVE pins. It also describes the function of the CLOCK input.

2.2.9.1 Chip Reset (RESET/)

This general purpose chip reset forces all the internal elements of the

LSI53C120 into a known state. It brings the State Machine to an idle

state and forces all controls to a passive state. The minimum RESET/

input asserted pulse width is 100 ns.

The LSI53C120 also contains an internal Power On Reset (POR)

function that is ORed with the chip reset pin. This eliminates the need

for an external chip reset if the power supply meets ramp up

specifications.

2.2.9.2 Warm Swap Enable (

WS_ENABLE/)

This input provides additional control capability for the LSI53C120. It

allows both the SCSI A-side bus and the SCSI B-side bus to be logically

disconnected. When the WS_ENABLE/ pin is asserted, after detection of

the next Bus Free state, the SCSI signals are 3-stated. This occurs so

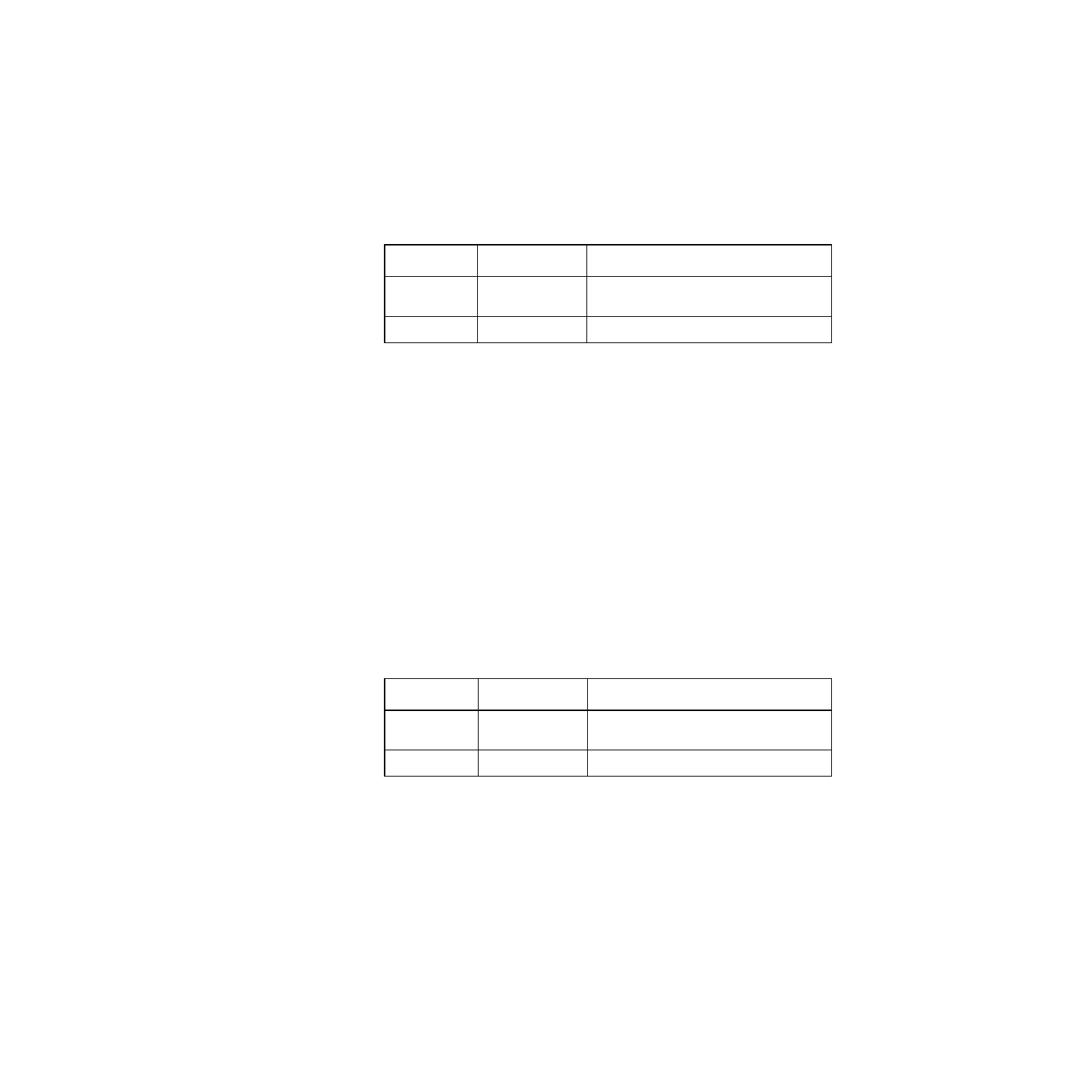

Table 2.3

DIFF_SENSE Control Signal Polarity

Signal Level

State

Effect

HIGH = 1

Asserted

The B-side drivers and receivers are

enabled.

LOW = 0

Deasserted

B-side drivers and receivers are disabled.

Table 2.4

RESET/ Control Signal Polarity

Signal Level

State

Effect

LOW = 0

Asserted

Reset is forced to all internal LSI53C120

elements.

HIGH = 1

Deasserted

LSI53C120 is not in a forced reset state.