B.10.2 ddr3 memory subsystem, B.10.3 ethernet mac engines, B.10.4 boot controller – Artesyn PCIE-8120 Installation and Use (July 2014) User Manual

Page 77: Table b-5, Ethernet physical interface mapping, Pcie-8120 hardware description

PCIE-8120 Hardware Description

PCIE-8120 Installation and Use (6806800R89C)

77

Precision clock synchronization on external references

Various Peripheral Interfaces Ethernet, serial/parallel hi-speed interfaces, TDM, Flash, and

so on. For details, see document OCT2200MDS8000 listed in

Table "Related Specifications"

B.10.2 DDR3 Memory Subsystem

The 32-bit DDR memory controller is used for interface to JEDEC DDR3 SDRAM devices. The

interface supports 4.32 GB/s at a 1080 MHz data rate (540 MHz clock rate).

The DSP memory on the PCIE-8120 is realized with two DDR3 x16 devices per DSP. The

memory access is 32-bits wide.

The default memory size is 512 MByte.

The DDR3 memory is not used until the DDR configuration is obtained from the boot image.

B.10.3 Ethernet MAC Engines

The OCT2224M device on the PCIE-8120 card configures two Ethernet MAC engines,

supporting 10/100/1000-Mbps data transfer rates on the physical interfaces: SERDES2 and

SERDES3 in SGMII mode. See

below.

EMAC0 and EMAC2 support jumbo packets (maximum size of 9,018 bytes or 9,022 bytes for

VLAN frames). EMAC2 is available for BOOTP.

B.10.4 Boot Controller

The boot controller is responsible for managing the boot process. The boot process loads a

boot image that is created by an Octasic software tool that allows the user to specify optional

device configuration and the application image to load.

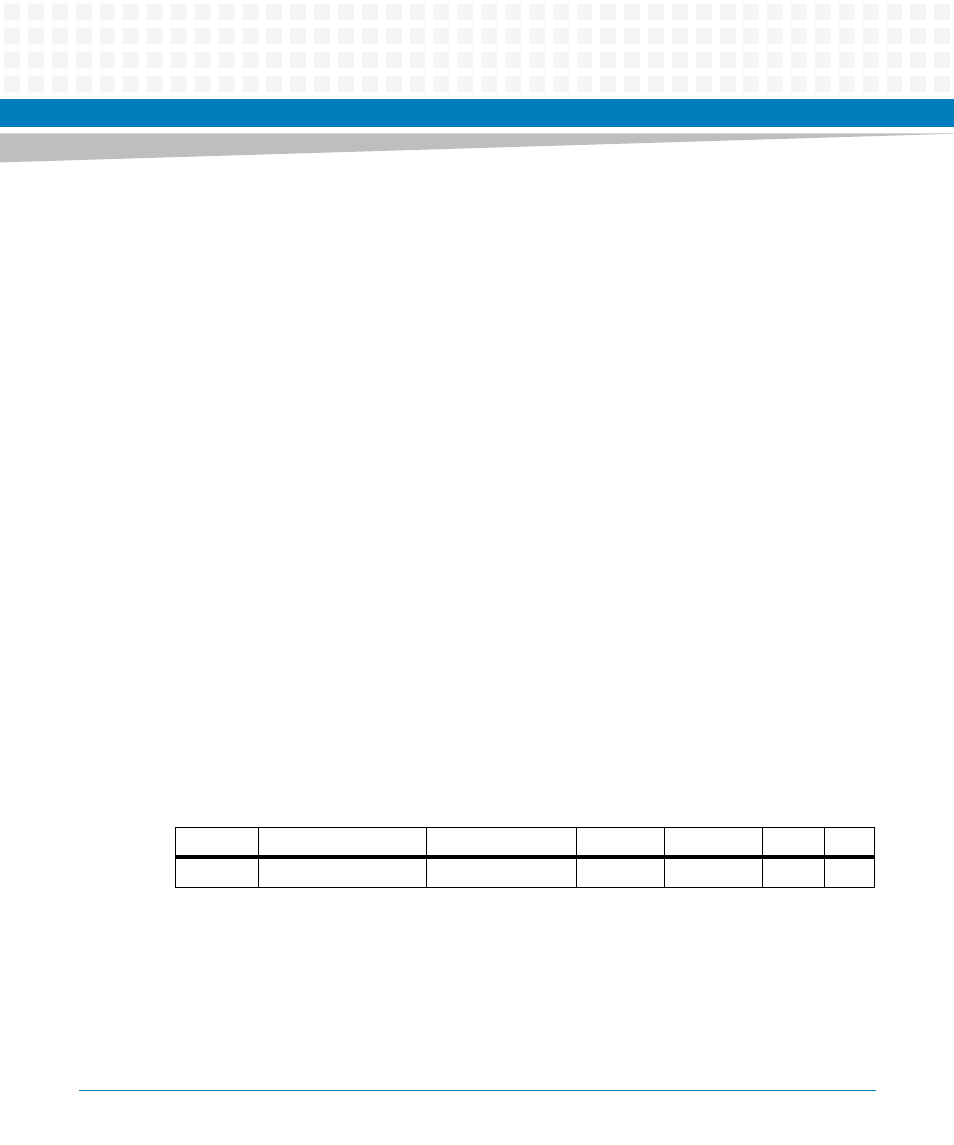

Table B-5 Ethernet Physical Interface Mapping

Mode

SERDES0

SERDES1

SERDES2

SERDES3

Eth0

Eth1

5

EMAC 1 (not used)

EMAC 3 (not used)

EMAC 2

EMAC 0

n/a

n/a