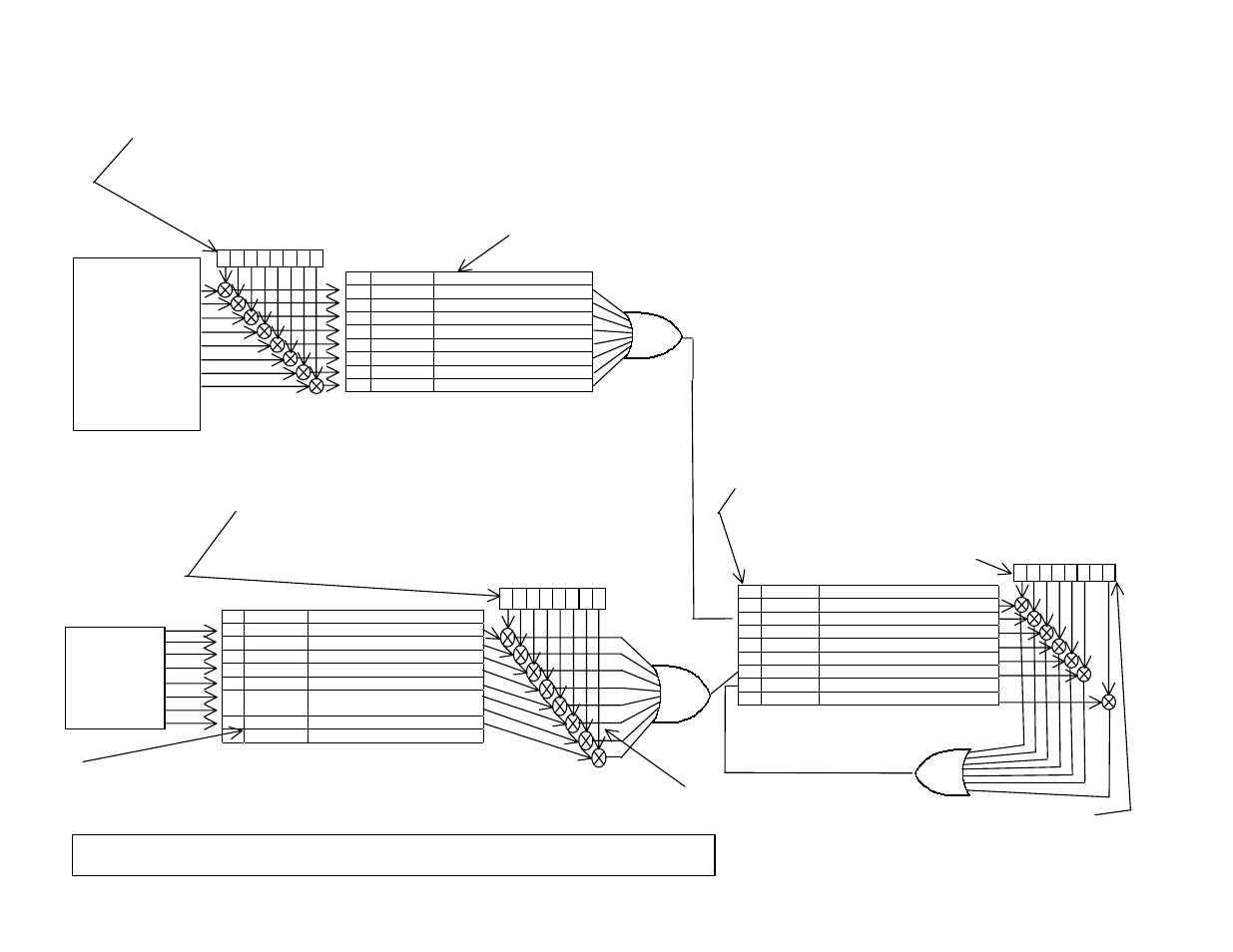

Scpi status implementation, Various events set the sesr bits directly – AMETEK SFA Series Programming Manual User Manual

Page 45

Various fault

events must be

enabled by the

protection

enable register

before they are

recorded in the

fault register.

Bit

Hex

Value Description

0

0x01

Not

used

1

0x02

Constant Current Operation

2

0x04

Converter

Fault

3

0x08

(Not

used).

4

0x10

Over Temperature Fault

5

0x20

External

Shutdown

6

0x40

Foldback Mode Operation

7

0x80

Remote Programming Error

Fault Register (also called the Protection Event Register).

Readable using the STAT:PROT:EVEN? query

The SCPI Status Byte. Read using either the *STB? command, or

the GPIB serial poll operation.

Bit

Hex

Value Description

0

0x01 Operation

Complete

1

0x02

Request Control (Not Used)

2

0x04

Query Error (Not Used)

3

0x08

Device Dependent Error

4

0x10

Execution Error (e.g., range error)

5

0x20

Command Error (e.g., syntax

error)

6

0x40

User Request (Not Used)

7

0x80

Power

On

Bit

Hex

Value Description

0

0x01

Not

Used

1

0x02

Protection Event Flag

2

0x04

Error/Event Queue Message Avail.

3

0x08

Questionable

Status (Not Used)

4

0x10

Message

Available

5

0x20

Standard

Event

Status Register

6

0x40

RQS/MSS Service Request Bit

7

0x80

Operation

Status Flag (Not Used)

Various

events set

the SESR

bits directly.

The SESR (Standard Event Service Register). Masking does not prevent events from

setting bits in the SESR. This facilitates polling as one means of detecting these events

since the SESR can be polled (read) using the *ESR? command, irrespective of the bits

set or not set in the Standard Event Status Enable Register.

The SESER (Standard Event Status Enable Register). This register is read

using the *ESE? SCPI query command. This register is written to using the

*ESE

corresponding bit from the SESR to pass through to the input of the OR gate

to be included in the SESR summary bit (bit 5) in the SCPI Status Byte.

The Service Request Enable Register (SRER).

Used to enable which Status Byte bits can affect the

service request bit. *SRE? reads. *SRE

Seven bit wise logical AND operations

Eight bit wise logical

AND operations

The Protection Enable Register. Readable using the STAT:PROT:ENAB? query command. Write-able using the STAT:PROT:ENAB

command. Used to select what fault events may set a bit in the Fault Register. Certain faults can occur even if they are not enabled. This is

because the Protection Enable Register merely filters which events are allowed to affect the Fault Register, not whether those events can

occur or not. An exception to this rule involves the Constant Voltage Operation, Constant Current Operation, and Foldback Mode Operation

bits. If these bits are not enabled, then mode changes shall not cause a shutdown. Read about these bits further in the manual.

SCPI STATUS IMPLEMENTATION