Figure 2–6, Bank 1 bank 2 bank 6 bank 5 – Altera Cyclone III LS FPGA Development Board User Manual

Page 29

Chapter 2: Board Components

2–21

Clock Circuitry

© October 2009 Altera Corporation

Cyclone III LS FPGA Development Board Reference Manual

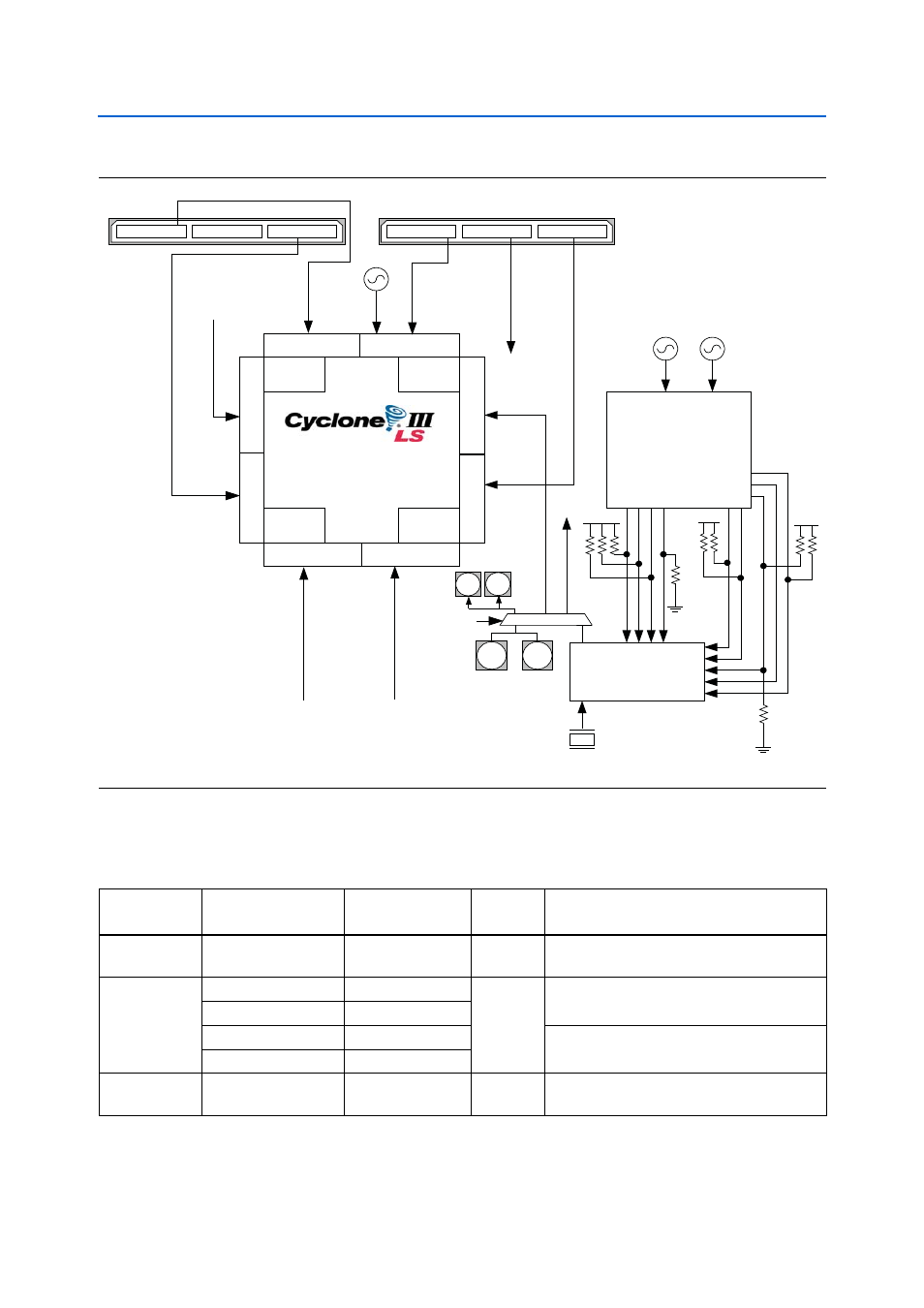

shows the external clock inputs for the Cyclone III LS FPGA development

board.

Figure 2–6. Cyclone III LS FPGA Development Board Clock Inputs

PLL 1

PLL 3

PLL 2

PLL 4

EP3CLS200F780

SMA

SMA

2-to-4 buffer

MAX II CPLD EPM2210

System Controller

25 MHz

Crystal

3.3 V

3.3 V

XIN 1

7 6 5 4 3 2 1 0

7 6 5 4 3 2 1 0

* CDCM61001 can be set to

ouput frequencies of 100 MHz,

125 MHz, 150 MHz, and 156.25 MHz

Low Jitter Clock

Generator*

(Default 125 MHz)

CDCM61001RHB

(2.5 V)

HSMB

HSMB

SMA

SMA

3 .3 V

Bank 8

Bank 7

Bank 3

Bank 4

Bank 1

Bank 2

Bank 6

Bank 5

HSMB_CLKIN_P[2]/N[2]

CLKIN_LEFT_P/N

(LVDS)

(LVDS)

HSMB_CLKIN0

CLKIN_66

(2.5 V)

(2.5 V)

HSMA_CLKIN0

(1.8 V)

66.6 MHz

HSMB_CLKIN_P[1]/N[1]

(LVDS)

HSMB_CLKIN_P[2]/N[2]

(LVDS)

EP3CLS70F780

Migratable to

ENET_RX_CLK

HSMB_CLKIN_P[1]/N[1]

(2.5 V)

(LVDS)

(2.5 V)

50 MHz

100 MHz

CLK_SEL

CLKIN_RIGHT_P/N

CLKIN_LEFT_P/N

(LVDS)

(LVDS)

PLL_R

S

T

n

PLL_CE

PLL_O

S

0

PLL_O

S

1

PLL_PR1

PLL_PR0

PLL_OD2

PLL_OD1

PLL_OD0

SMA Clock Output

SMA Clock Output

(LVDS)

(LVPECL)

Table 2–20. Cyclone III LS FPGA Development Board Clock Inputs (Part 1 of 2)

Source

Schematic Signal

Name

Cyclone III LS

Device Pin Number

I/O

Standard

Description

X3

CLKIN_66

B16

1.8-V

66.6 MHz oscillator used for the memories or

general purpose clock input.

SMA or

125.000 MHz

(Default

Frequency)

CLKIN_LEFT_P

N2

LVDS

Input to the fan-out buffer (U20) which drives

LVDS input to the left edge of PLL input.

CLKIN_LEFT_N

N1

CLKIN_RIGHT_P

N27

Input to the fan-out buffer (U20) which drives

LVDS input to the right edge of PLL input.

CLKIN_RIGHT_N

N28

Samtec HSMC

HSMA_CLKIN0

A16

LVTTL

Single-ended input from the installed HSMC

port A cable or board.