Altddio_out ip core signals – Altera Double Data Rate I/O User Manual

Page 18

Name

Require

d

Description

sset

No

Synchronous set input. The

sclr

and

sset

ports cannot be connected at the

same time. The

sset

port is available for Arria GX, Stratix III, Stratix II,

Stratix II GX, Stratix, Stratix GX, HardCopy II, and HardCopy Stratix devices

only.

(1)

Table 5: ALTDDIO_IN Output Ports

Name

Require

d

Description

dataout_h[]

Yes

Data sampled from

datain[]

port at the rising edge of the

inclock

signal.

dataout_l[]

Yes

Data sampled from

datain[]

port at the falling edge of the

inclock

signal.

ALTDDIO_OUT IP Core Signals

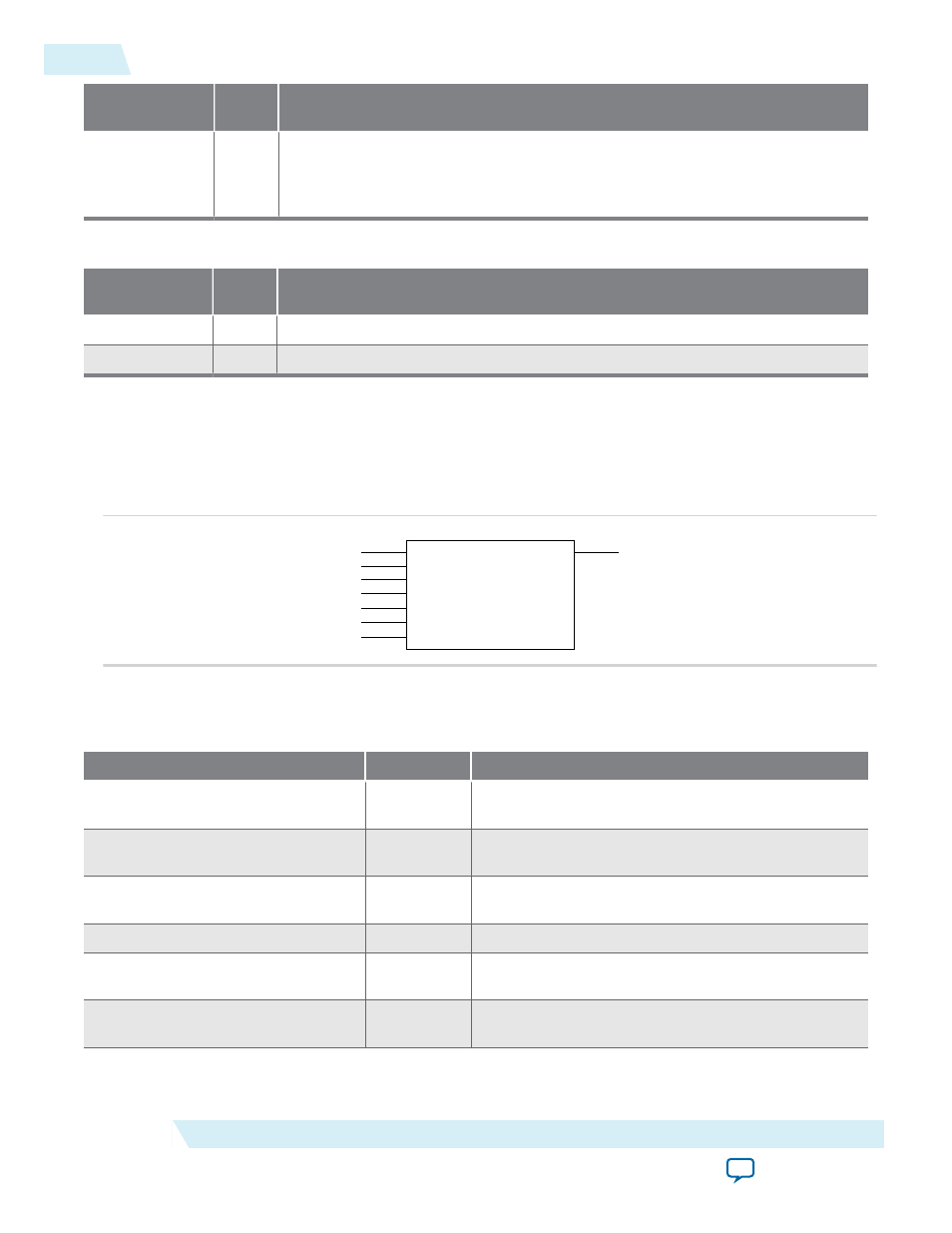

This figure shows the ports for the ALTDDIO_OUT IP core.

Figure 10: ALTDDIO_OUT Signals

datain_h[ ]

outclock

outclocken

aclr

aset

dataout[ ]

altddio_out

datain_l[ ]

oe

These tables list the input and output ports for the ALTDDIO_OUT IP core.

Table 6: ALTDDIO_OUT Input Ports

Name

Required

Description

datain_h[]

Yes

Input data for rising edge of

outclock

port. Input

port

WIDTH

wide.

datain_l[]

Yes

Input data for falling edge of

outclock

port. Input

port

WIDTH

wide.

outclock

Yes

Clock signal to register data output.

dataout

port

outputs DDR data on each level of

outclock

signal.

outclocken

No

Clock enable for

outclock

port.

aclr

No

Asynchronous clear input. The

aclr

and

aset

ports

cannot be connected at the same time.

aset

No

Asynchronous set input. The

aclr

and

aset

ports

cannot be connected at the same time.

18

ALTDDIO_OUT IP Core Signals

UG-DDRMGAFCTN

2015.01.23

Altera Corporation

Double Data Rate I/O (ALTDDIO_IN, ALTDDIO_OUT, and ALTDDIO_BIDIR) IP Cores User Guide