Create a divider – Altera Double Data Rate I/O User Manual

Page 15

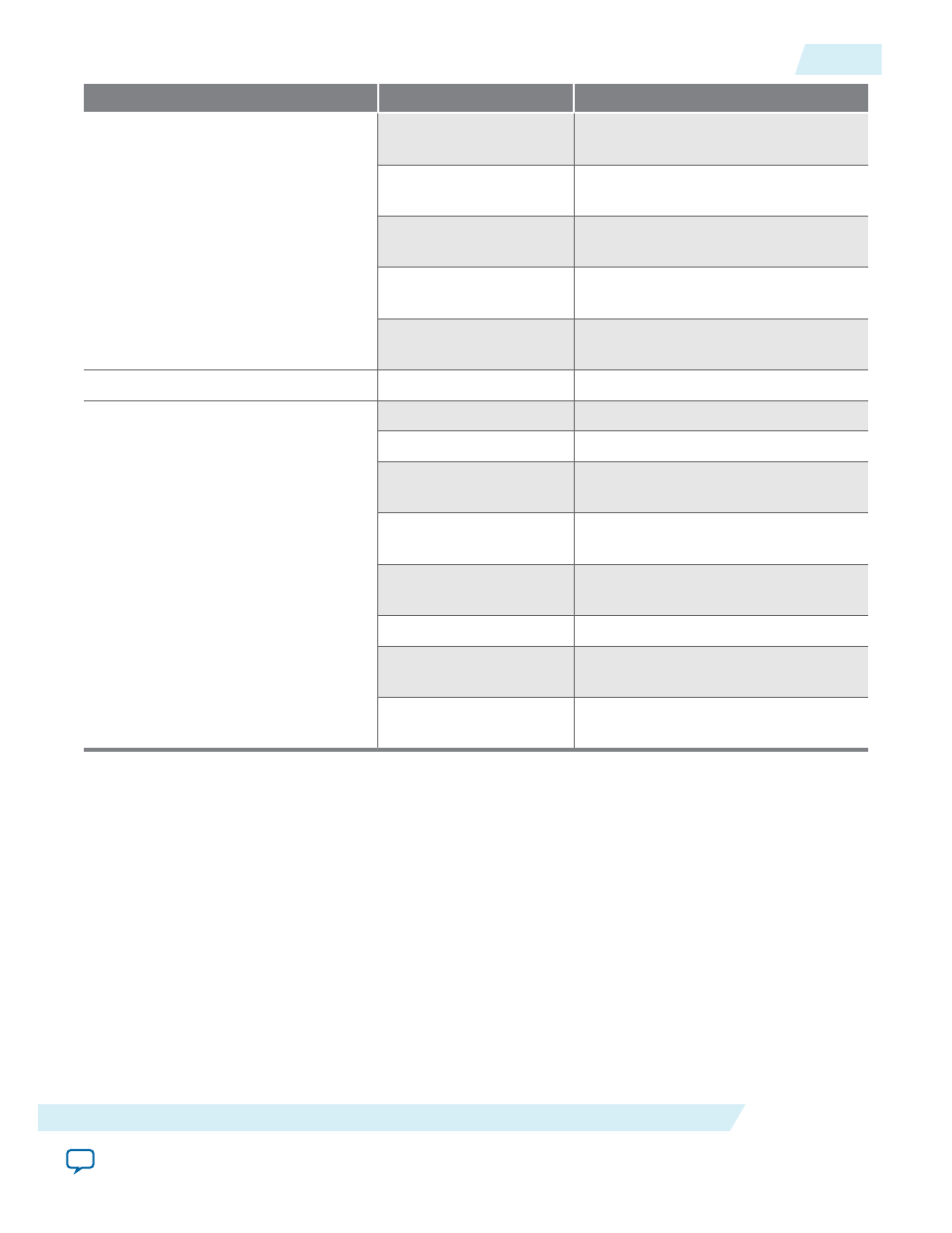

Parameter Editor Page

Parameter

Value

4

Do you want to pipeline

the function?

Select Yes, I want an output latency

of 1 clock cycle

Create an Asynchronous

Clear input

Turned off

Create a Clock Enable

input

Turned off

Which do you wish to

optimize?

Select Default Optimization

Always return a positive

remainder?

Select Yes

5

Generate netlist

Turned off

6

Variation file

Turned on

Quartus II IP file

Turned on

Quartus II symbol file

(.bsf)

Turned off

Instantiation template

file

Turned on

Verilog HDL black box

file (_bb.v)

Turned on

AHDL Include file (.inc) Turned off

VHDL component

declaration file (.cmp)

Turned on

PinPlanner ports file

(.PPF)

Turned on

4. Click Finish.

The

lpm_divide

module is now built.

Create a Divider

Use the following steps to combine the

ALTDDIO_BIDIR

and

lpm_divide

modules to create a divider.

Follow these steps to create a top-level VHDL file:

1. In the Quartus II software, with the ex2.qar project open, open the file ex2.vhd.

2. On the Project menu, click Add/Remove File in Project. The File Settings page displays.

3. In the File Settings window, click (...) after File name and browse for ex2.vhd in the project folder.

4. Select ex2.vhd and click Add.

5. Click OK.

The top-level file is added to the project. You have now created the complete design file.

UG-DDRMGAFCTN

2015.01.23

Create a Divider

15

Double Data Rate I/O (ALTDDIO_IN, ALTDDIO_OUT, and ALTDDIO_BIDIR) IP Cores User Guide

Altera Corporation