Altmult_complex ports, Altmult_complex ports -2 – Altera MAX 10 Embedded Multipliers User Manual

Page 35

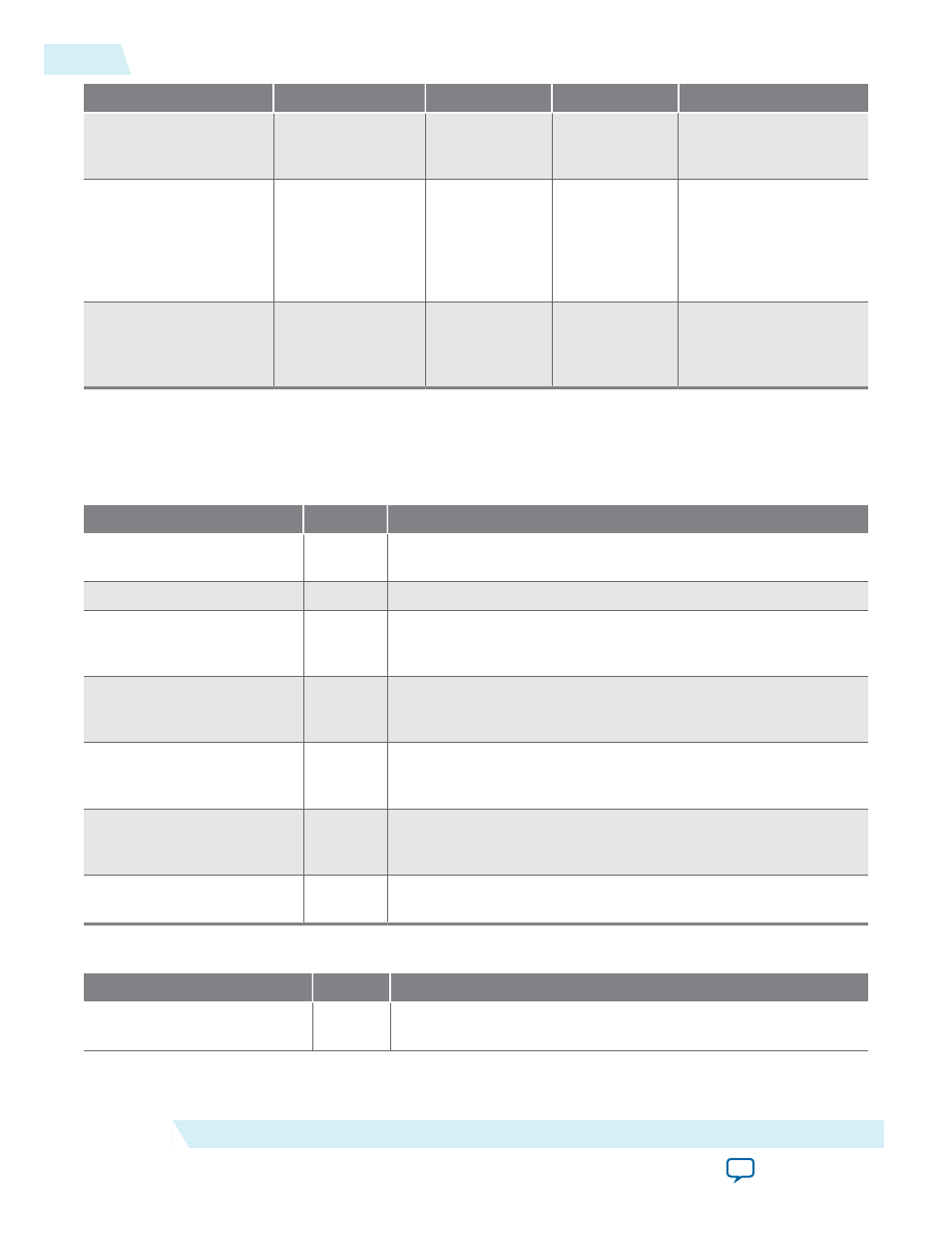

GUI Parameter

Parameter

Condition

Value

Description

Output latency []

clock cycles

PIPELINE

—

0–14

Specifies the number

of clock cycles for

output latency.

Create an asynchro‐

nous Clear input

—

—

On or off

Specifies synchronous

clear for the complex

multiplier. Clears the

function asynchro‐

nously when the

aclr

port is asserted high.

Create clock enable

input

—

—

On or off

Specifies active high

clock enable for the

clock port of the

complex multiplier.

ALTMULT_COMPLEX Ports

Table 7-3: ALTMULT_COMPLEX IP Core Input Ports

Port Name

Required

Description

aclr

No

Asynchronous clear for the complex multiplier. When the

aclr

port is asserted high, the function is asynchronously cleared.

clock

Yes

Clock input to the ALTMULT_COMPLEX function.

dataa_imag[]

Yes

Imaginary input value for the data

A

port of the complex

multiplier. The size of the input port depends on the

WIDTH_A

parameter value.

dataa_real[]

Yes

Real input value for the data

A

port of the complex multiplier.

The size of the input port depends on the

WIDTH_A

parameter

value.

datab_imag[]

Yes

Imaginary input value for the data

B

port of the complex

multiplier. The size of the input port depends on the

WIDTH_B

parameter value.

datab_real[]

Yes

Real input value for the data

B

port of the complex multiplier.

The size of the input port depends on the

WIDTH_B

parameter

value.

ena

No

Active high clock enable for the clock port of the complex

multiplier.

Table 7-4: ALTMULT_COMPLEX IP Core Output Ports

Port Name

Required

Description

result_imag

Yes

Imaginary output value of the multiplier. The size of the output

port depends on the

WIDTH_RESULT

parameter value.

7-2

ALTMULT_COMPLEX Ports

UG-M10DSP

2014.09.22

Altera Corporation

ALTMULT_COMPLEX (Complex Multiplier) IP Core References