Lpm_mult ports, Lpm_mult ports -3 – Altera MAX 10 Embedded Multipliers User Manual

Page 15

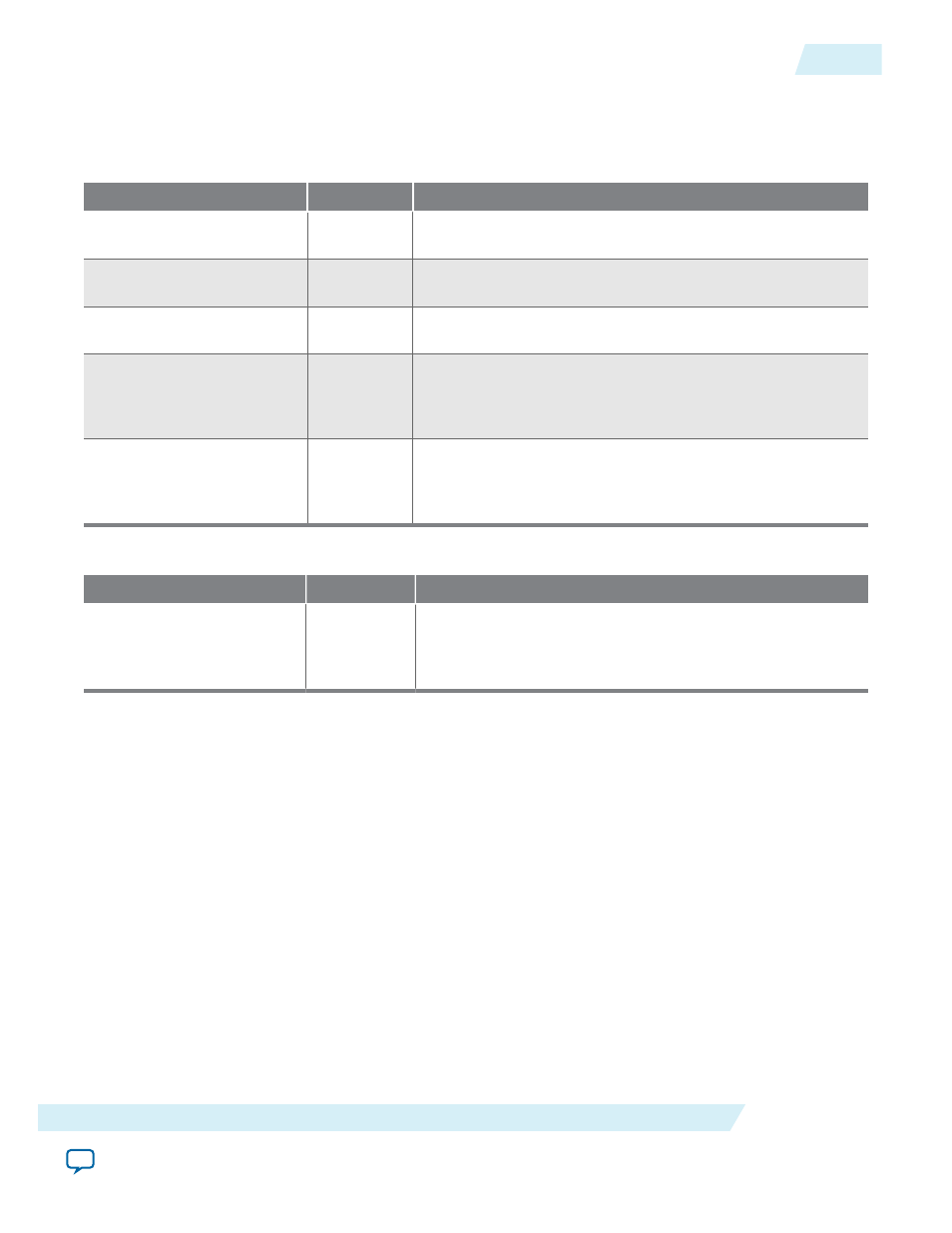

LPM_MULT Ports

Table 4-4: LPM_MULT IP Core Input Ports

Port Name

Required

Description

dataa[]

Yes

Data input. The size of the input port depends on the

LPM_

WIDTHA

parameter value.

datab[]

Yes

Data input. The size of the input port depends on the

LPM_

WIDTHB

parameter value.

clock

No

Clock input for pipelined usage. For

LPM_PIPELINE

values

other than

0

(default), the clock port must be enabled.

clken

No

Clock enable for pipelined usage. When the

clken

port is

asserted high, the adder/subtractor operation takes place.

When the signal is low, no operation occurs. If omitted, the

default value is

1

.

aclr

No

Asynchronous clear port used at any time to reset the

pipeline to all

0

s, asynchronously to the clock signal. The

pipeline initializes to an undefined (X) logic level. The

outputs are a consistent, but non-zero value.

Table 4-5: LPM_MULT IP Core Output Ports

Port Name

Required

Description

result[]

Yes

Data output. The size of the output port depends on the

LPM_WIDTHP

parameter value. If

LPM_WIDTHP

< max (

LPM_

WIDTHA

+

LPM_WIDTHB

,

LPM_WIDTHS

) or (

LPM_WIDTHA

+

LPM_

WIDTHS

), only the

LPM_WIDTHP

MSBs are present.

UG-M10DSP

2014.09.22

LPM_MULT Ports

4-3

LPM_MULT (Multiplier) IP Core References

Altera Corporation