Altmult_add ports, Altmult_add ports -8 – Altera MAX 10 Embedded Multipliers User Manual

Page 32

GUI Parameter

Parameter

Condition

Value

Description

What is the source for

asynchronous clear

input?

MULTIPLIER_

ACLR[]

• Output

Configuration

> Register

output of the

multiplier =

On

• Output

Configuration

> More

Options

• Aclr0–Aclr2

• None

Specifies the source for

asynchronous clear

input.

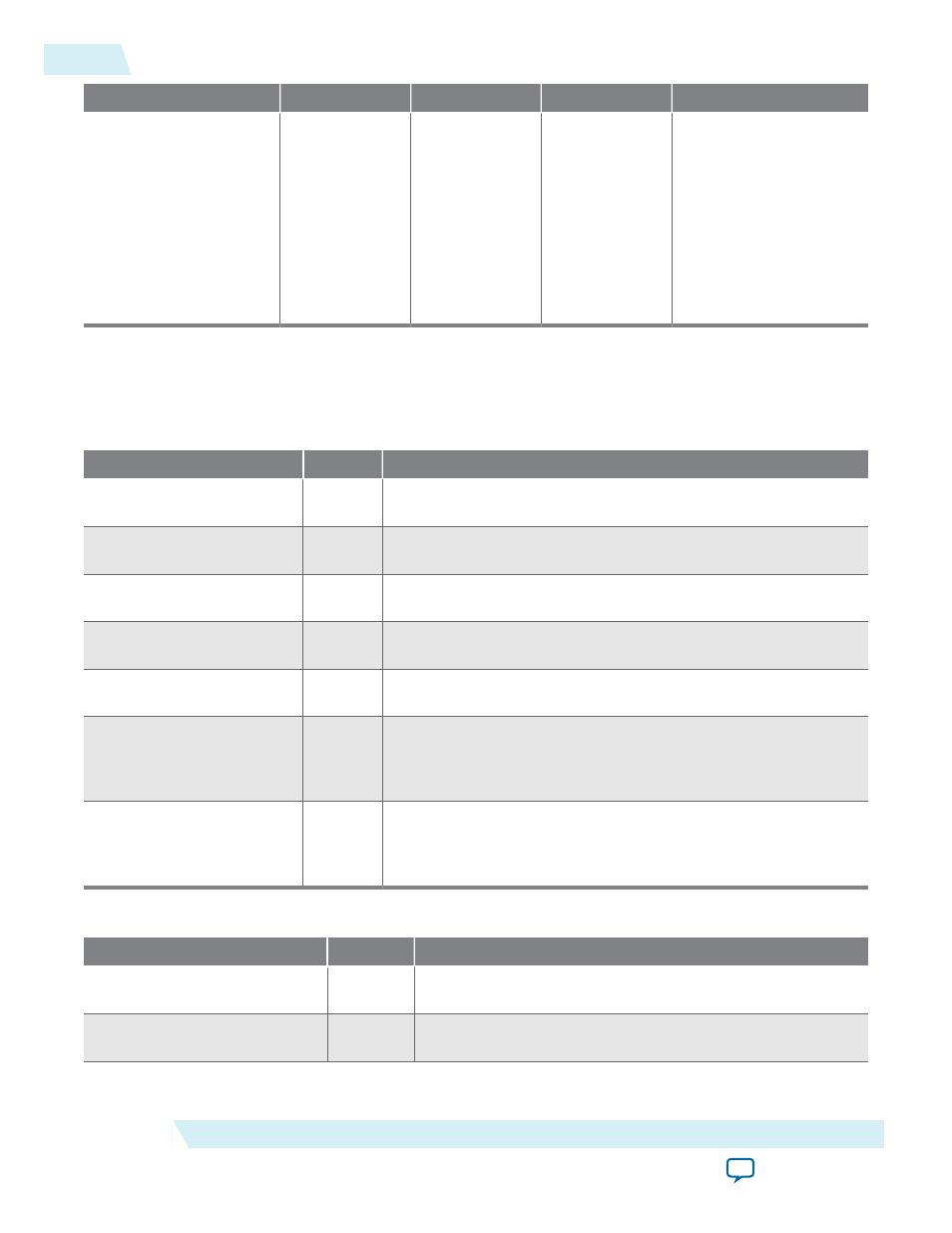

ALTMULT_ADD Ports

Table 6-4: ALTMULT_ADD IP Core Input Ports

Port Name

Required

Description

dataa[]

Yes

Data input to the multiplier. Input port

[NUMBER_OF_

MULTIPLIERS * WIDTH_A - 1..0]

wide.

datab[]

Yes

Data input to the multiplier. Input port

[NUMBER_OF_

MULTIPLIERS * WIDTH_B - 1..0]

wide.

clock[]

No

Clock input port

[0..3]

to the corresponding register. This port

can be used by any register in the IP core.

aclr[]

No

Input port

[0..3]

. Asynchronous clear input to the

corresponding register.

ena[]

No

Input port

[0..3]

. Clock enable for the corresponding clock[]

port.

signa

No

Specifies the numerical representation of the

dataa[]

port. If the

signa

port is high, the multiplier treats the

dataa[]

port as a

signed two's complement number. If the

signa

port is low, the

multiplier treats the

dataa[]

port as an unsigned number.

signb

No

Specifies the numerical representation of the

datab[]

port. If the

signb

port is high, the multiplier treats the

datab[]

port as a

signed two's complement number. If the

signb

port is low, the

multiplier treats the

datab[]

port as an unsigned number.

Table 6-5: ALTMULT_ADD IP Core Output Ports

Port Name

Required

Description

result[]

Yes

Multiplier output port. Output port

[WIDTH_RESULT -

1..0]

wide.

overflow

No

Overflow flag. If

output_saturation

is enabled, overflow

flag is set.

6-8

ALTMULT_ADD Ports

UG-M10DSP

2014.09.22

Altera Corporation

ALTMULT_ADD (Multiply-Adder) IP Core References