B - sample programs, Sample programs, Appendix – Rockwell Automation 1771-VHSC , D17716.5.74 Very High S User Manual

Page 54: Sample program for plc-2 family processors

Appendix

B

Sample Programs

Sample Program for PLC-2 Family Processors

5

333

333

G

G

G

G

334

400

405

333

402

0

01

281

7

3

0

0

<

333

G

G

400

401

405

334

0

00

3

568

281

6

=

334

281

=

333

G

G

402

334

405

403

0

02

7

281

429

403

429

7

=

=

<

<

<

405

405

04

00

8

405

01

405

02

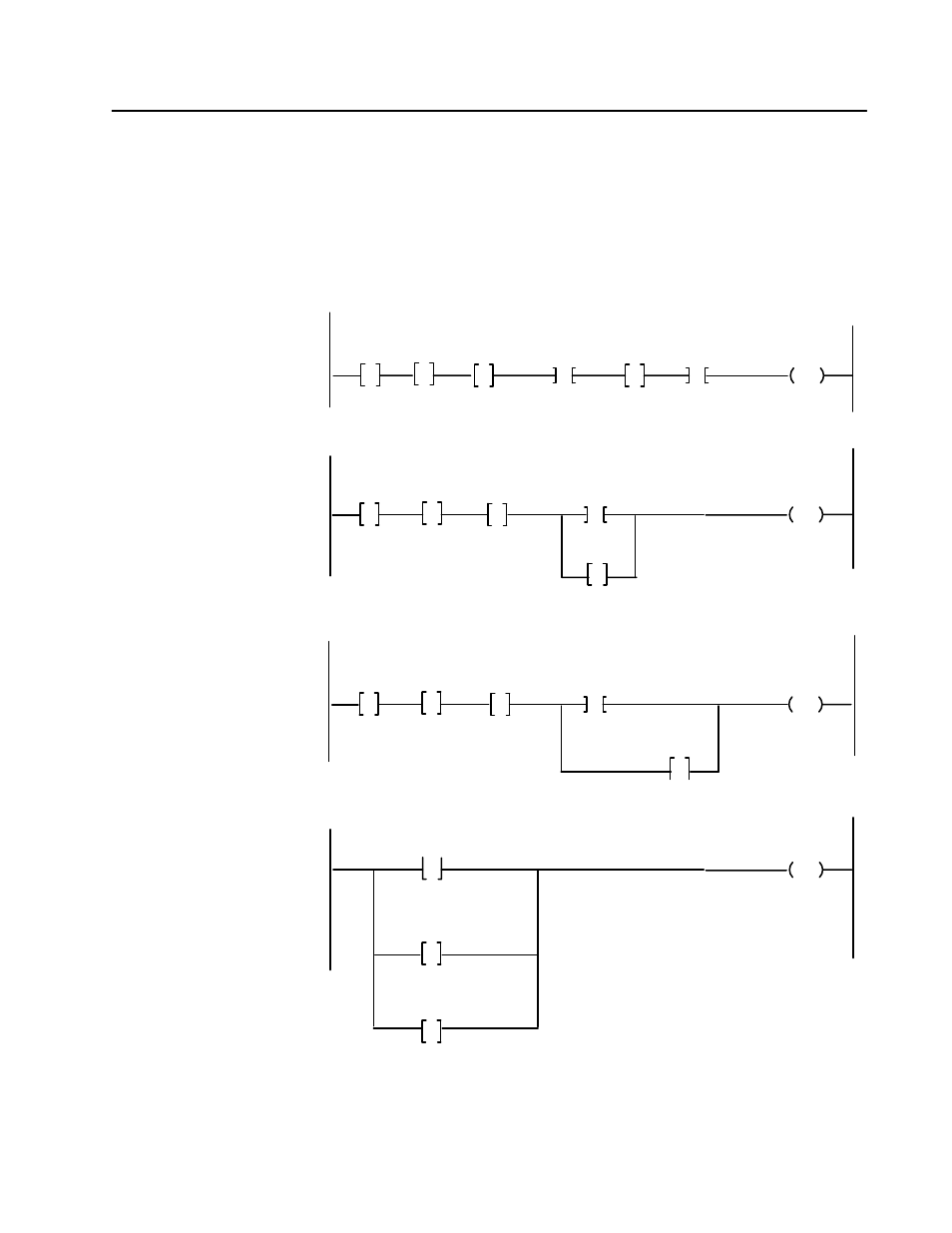

These rungs illustrate a method of monitoring the count for values greater than 3 digits. The total count is displayed in words 333 and 334.

This rung set storage bit 405/1 when the count is between the MSD lower limit and the MSD upper limit.

(MSDLL) < Count 0 < (MSDUL)

MSD

Count 0

Store bit count 0

between MSDLL

and MSDUL

When counting up, this rung will go true first. Bit 405/00 will be set when count 0 is equal to the MSDLL and greater than or equal to the LSDLL. (Count 0 = MSDLL) +

(LSDLL < = Count 0)

Store LSD

lower limit

LSD Count 0

Store bit

Count 0 > = LSDLL

LSD Count 0

When counting up, this rung will go true last. Bit 405/02 will be set when count 0 is equal to the MSDUL and less than or equal to the LSDUL. (Count 0 = MSDUL) + (Count

0 < = LSDUL)

Store MSD

upper limit

LSD Count 0

Store LSD

upper limit

Store bit

Count 0 < = LSDUL

When using all 3 storage bits, bit 405/4 represents when count 0 is within the specified range. In this particular case, when the count is

between 3,568 and 7,429

Store bit count 0 between

MSDLL and MSDUL

Store bit count 0 < = LSDUL

Store bit count 0

within desired range

Store bit count 0 > = LSDLL

Store MSD

lower limit

MSD

Count 0

LSD

Count 0

MSD

Count 0

Store MSD

upper limit

MSD

Count 0

Store MSD

lower limit

MSD

Count 0

Store LSD

upper limit