Rockwell Automation 1203-SM1 SLC to SCANport Communication Module User Manual

Page 59

M0, M1, and G Files

A–3

Publication 1203–5.9 –– October 1996

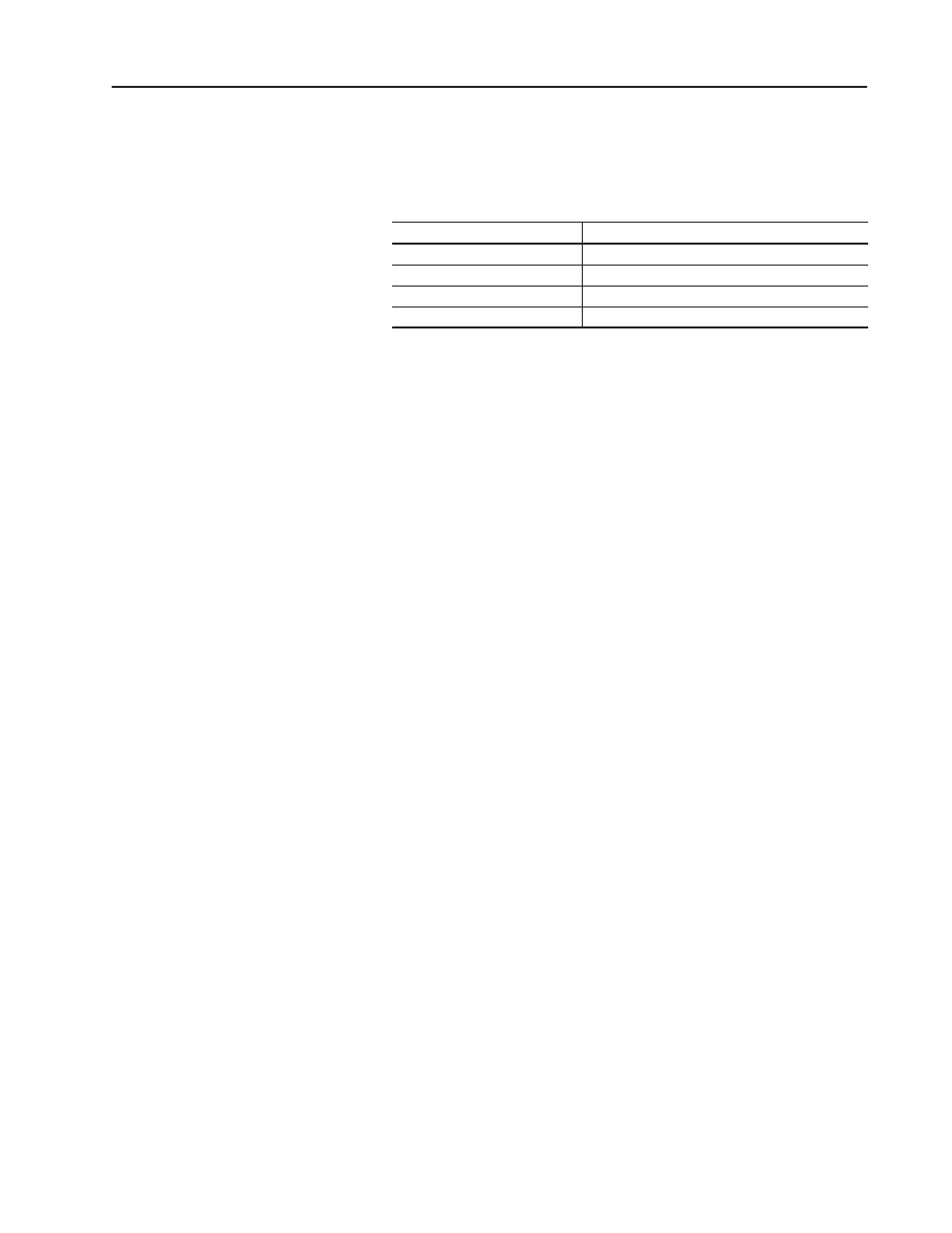

Restrictions on Using M0–M1 Data File Addresses

You can use M0 and M1 data file addresses in all instructions except

the OSR instruction and the following instruction parameters:

Instruction

Parameter (uses file indicator #)

BSL, BSR

File (bit array)

SQO, SQC, SQL

File (sequencer file)

LFL, LFU

LIFO (stack)

FFL, FFU

FIFO (stack)

Monitoring Bit Addresses

For SLC 5/02 processors, the M0/M1 monitoring option is always

disabled. (This processor does not let you monitor the actual state of

each addressed M0/M1 address.) For SLC 5/03 and SLC 5/04

processors, you can choose to disable or enable the monitoring

option by selecting F6, System Config, from the APS main menu.

M0/M1 Monitoring Option Disabled

When you monitor a ladder program in the Run or Test mode with

the M0/M1 monitoring option disabled, the following bit

instructions, addressed to an M0 or M1 file, are indicated as false

regardless of their actual true/false logical state.

Mf:e.s Mf:e.s Mf:e.s Mf:e.s Mf:e.s

–––] [–– –––]/[–– –––( )–– ––(L)–– –––(U)––

b b b b b

f= file (0 or 1)

When you are monitoring the ladder program in the Run or Test mode, the

APS or HHT display does not show these instructions as being true when

the processor evaluates them as true.