Interfacing to the lsm continued – Rockwell Automation 1402-LSM Line Synchronization Module Installation Instructions User Manual

Page 40

Chapter 4

Application Information

4–6

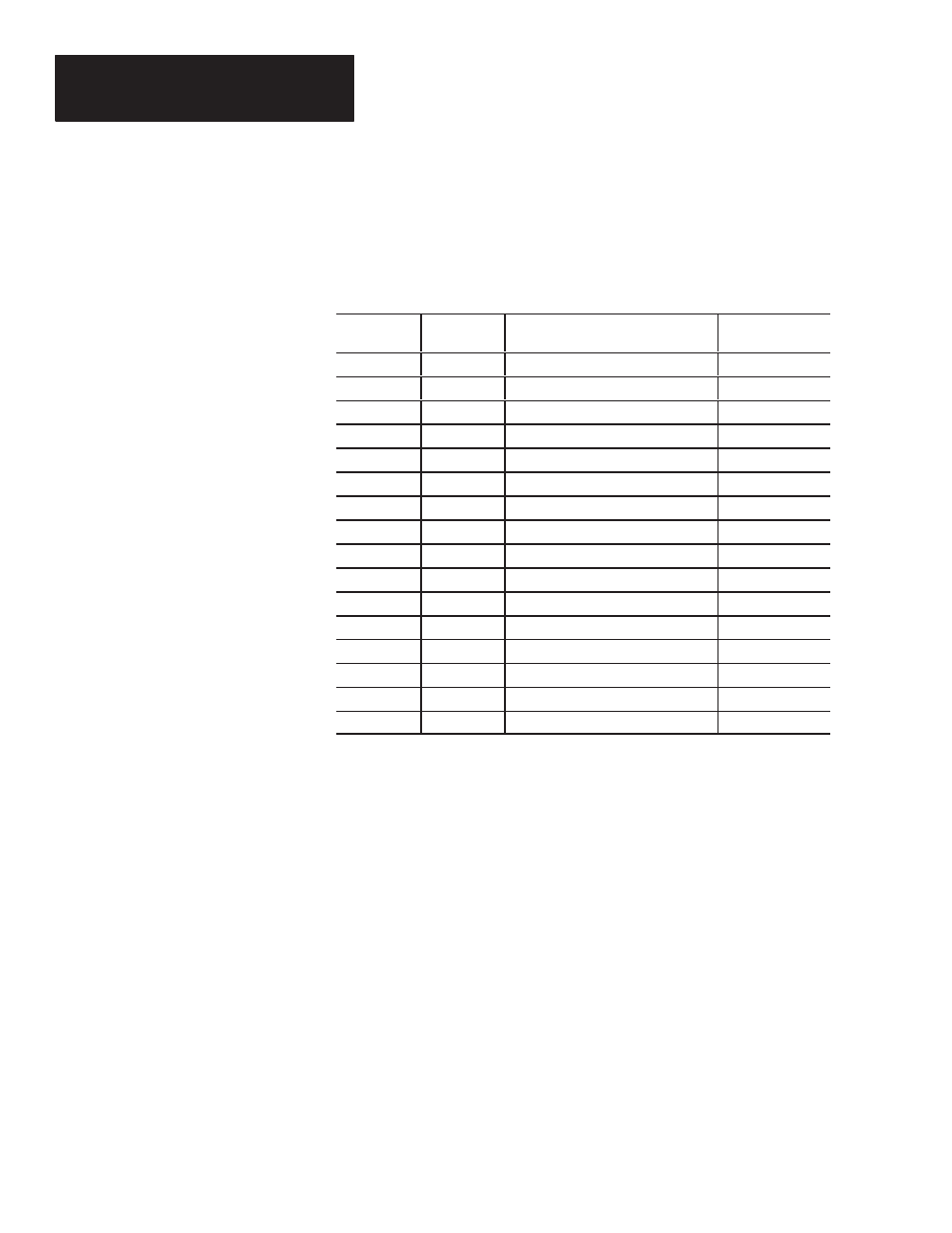

Discrete Inputs to the PLC–5

The discrete inputs to the PLC–5 are as follows:

Table 4.3

Octal Bit

Number

Decimal Bit

Number

Input Description

State Values

17

15

Module Status

1 = Module Failed

16

14

Raise Voltage

1 = Raise

15

13

Lower Voltage

1 = Lower

14

12

Raise Speed – Frequency Adjust

1 = Raise

13

11

Lower Speed – Frequency Adjust

1 = Lower

12

10

Raise Speed – Phase Adjust

1 = Raise

11

9

Lower Speed – Phase Adjust

1 = Lower

10

8

Raise Power – Load Share Adjust

1 = Raise

7

7

Reserved

N/A

6

6

Reserved

N/A

5

5

Reserved

N/A

4

4

Reduce Power – Load Share Adjust

1 = Lower

3

3

Close Breaker

1 = Close Breaker

2

2

Synchronization Failure

1 = Failure

1

1

Powered Up Bit

1 = Module Ready

0

0

Reserved

N/A

The Module Status discrete input to the PLC–5 when set to 1 indicates that

the LSM has identified a potential problem. A value of 0 indicates normal

operation of the LSM. Additional information pertaining to the cause of the

problem may be obtained by reading the appropriate block transfer data from

the “Diagnostic Parameters” Table B.11. (See Appendix B, “Block Transfer

Tables and Discrete I/O Definition”, for additional information.)

If the Module Status discrete input to the PLC–5 is set to 1, all block transfer

writes will be ignored and only the Diagnostic Parameters block transfer read

will return valid data. Any other block transfers should not be executed at

this time.

The Raise Voltage synchronization error discrete input to the PLC–5

indicates that the Synchronizing Bus has a lower voltage level than that of

the Reference Bus.

The Lower Voltage synchronization error discrete input to the PLC–5

indicates that the Synchronizing Bus has a higher voltage level than that of

the Reference Bus.

The Raise Speed – Frequency Adjust synchronization error discrete input to

the PLC–5 indicates that the Synchronizing Bus is producing voltage at a

frequency lower than that of the Reference Bus.

Interfacing to the LSM Continued