Configuration by eeprom, 1 pin descriptions, 2 eeprom hardware interface – Cirrus Logic CS5376A User Manual

Page 26: 3 eeprom organization, Figure 14. eeprom configuration block diagram, Cs5376a

CS5376A

26

DS612F4

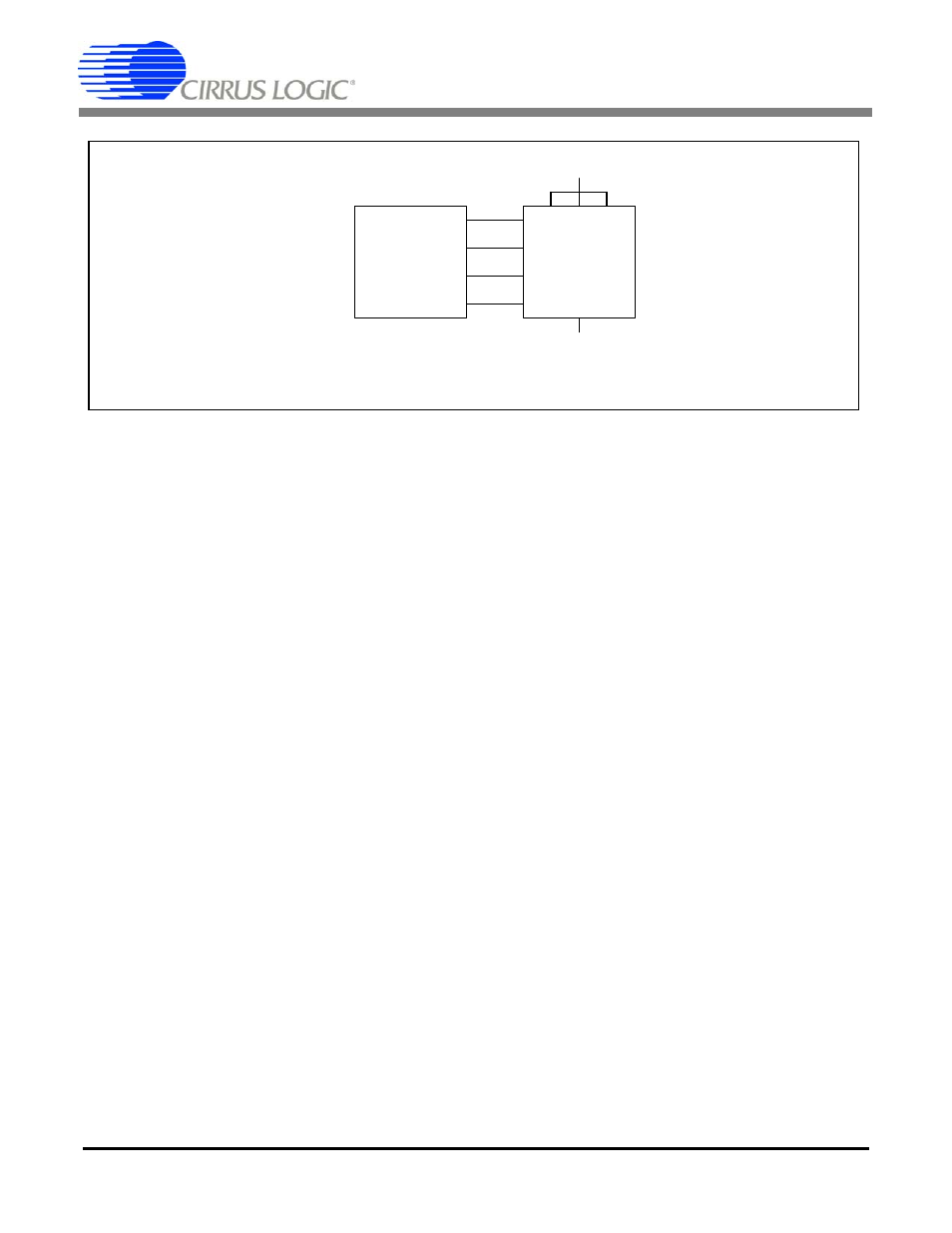

8. CONFIGURATION BY EEPROM

After reset, the CS5376A reads the state of the

BOOT pin to determine a source for configuration

commands. If BOOT is high, the CS5376A ini-

tiates serial transactions through the SPI 1 port to

read configuration information from an external

EEPROM.

8.1 Pin Descriptions

Pins required for EEPROM boot are listed here,

other SPI 1 pins are inactive.

GPIO11:EECS - Pin 46

EEPROM chip select output, active low.

SCK1 - Pin 48

Serial clock output, nominally 1.024 MHz.

MOSI - Pin 51

Serial data output pin. Valid on rising edge of

SCK1, transition on falling edge.

MISO - Pin 50

Serial data input pin. Valid on rising edge of SCK1,

transition on falling edge.

8.2 EEPROM Hardware Interface

When booting from EEPROM the CS5376A SPI 1

port actively performs serial transactions, as shown

in Figure 15, to read configuration commands and

data. 8-bit SPI opcodes and 16-bit addresses are

combined to read back 8-bit configuration com-

mands and 24-bit configuration data.

System design should include a connection to the

configuration EEPROM for in-circuit reprogram-

ming. The CS5376A SPI 1 pins go high impedance

when inactive to support external connections to

the serial bus.

8.3 EEPROM Organization

The boot EEPROM holds the 8-bit commands and

24-bit data required to initialize the CS5376A into

an operational state. Configuration information

starts at memory location 0x10, with addresses

0x00 to 0x0F free for use as manufacturing header

information.

The first serial transaction reads a 1-byte command

from memory location 0x10 and then, depending

on the command type, reads multiple 3-byte data

words to complete the command. Command and

data reads continue until the ‘Filter Start’ command

is recognized.

The maximum number of bytes that can be written

for a single configuration is approximately

GPIO11:EECS

SCK1

MISO

MOSI

CS5376A

AT25640

CS

SCK

SI

SO

46

48

50

51

1

6

2

5

VD

GND

WP

VCC HOLD

3

8

7

4

Figure 14. EEPROM Configuration Block Diagram