Filter register 5, Filter register 6, Teletext register 0 – Cirrus Logic CS4955 User Manual

Page 49: Teletext register 1

CS4954 CS4955

DS278F6

49

F

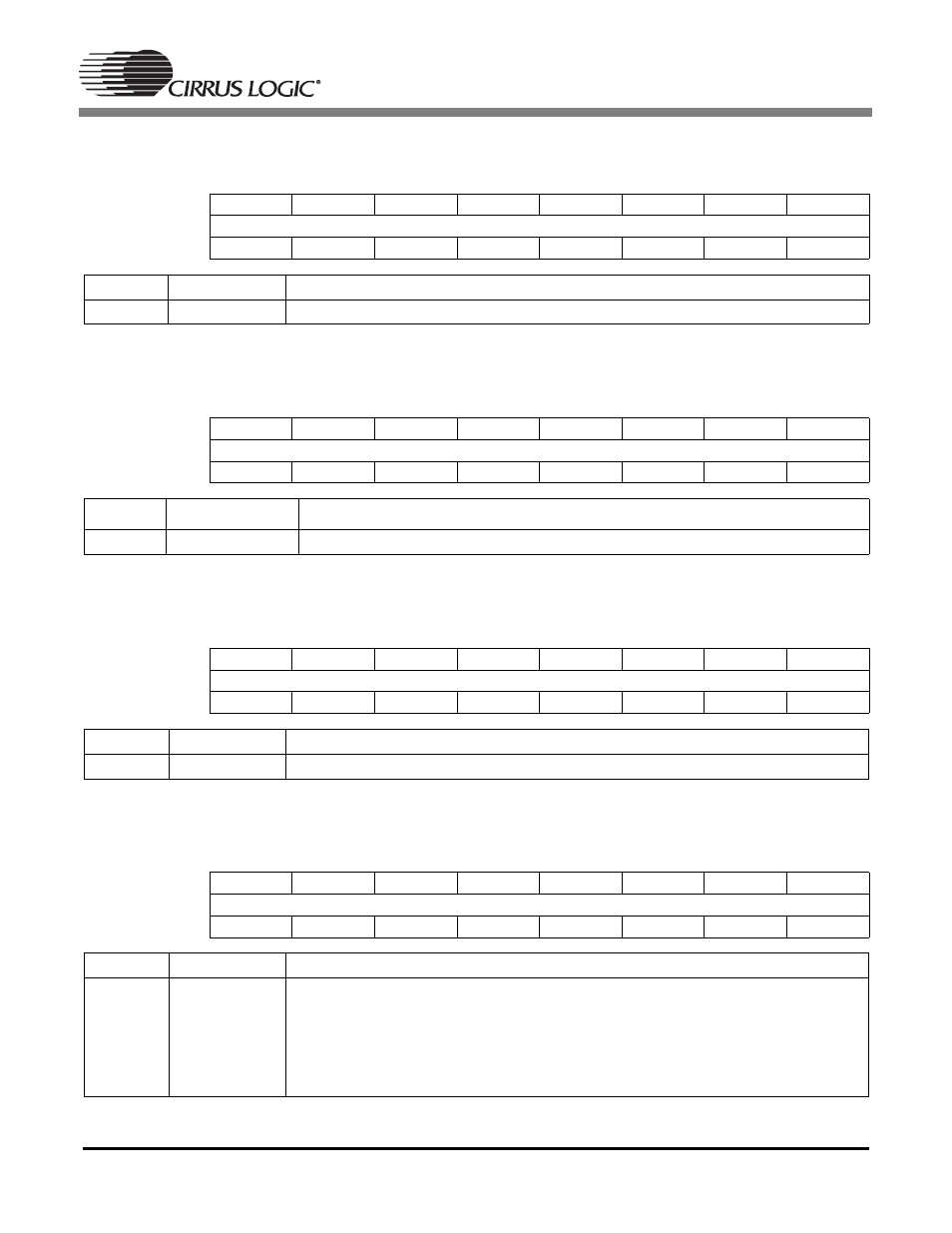

ilter Register 5

Address

0

×

27

B_AMP

Read/Write

Default Value = 80h

F

ilter Register 6

Address

0

×

28

Bright_Offsett Read/Write

Default Value = 00h

Teletext Register 0

Address

0

×

29

TTXHS

Read/Write

Default Value = A1h

T

eletext Register 1

Address

0

×

2A

TTXHD

Read/Write

Default Value = 02h

Bit Number

7

6

5

4

3

2

1

0

Bit Name

B_AMP

Default

1

0

0

0

0

0

0

0

Bit

Mnemonic

Function

7:0

B_AMP

Blue amplitude coefficient

Bit Number

7

6

5

4

3

2

1

0

Bit Name

BRIGHTNESS_OFFSET

Default

0

0

0

0

0

0

0

0

Bit

Mnemonic

Function

7:0

BRGHT_OFFSET

Brightness adjustment ( range: -128 to +127)

Bit Number

7

6

5

4

3

2

1

0

Bit Name

TTXHS

Default

1

0

1

0

0

0

0

1

Bit

Mnemonic

Function

7:0

TTXHS

Start of teletext request pulses or start of window

Bit Number

7

6

5

4

3

2

1

0

Bit Name

TTXHD

Default

0

0

0

0

0

0

1

0

Bit

Mnemonic

Function

7:0

TTXHD

If TTX_WINDOW = 0 then this register is used as the Pipeline delay between

TTXRQ and TTXDAT signals in the teletext source. User programmable delay step

of 37 ns per LSB.

If TTX_WINDOW = 1 then this register is used as the 8 LSBs of the teletext insertion

windows; the 3 MSBs are located in register 0×31. (register 0×31 bit 3)