9 pal progressive scan, 3 itu-r.bt656, Itu-r.bt656 – Cirrus Logic CS4955 User Manual

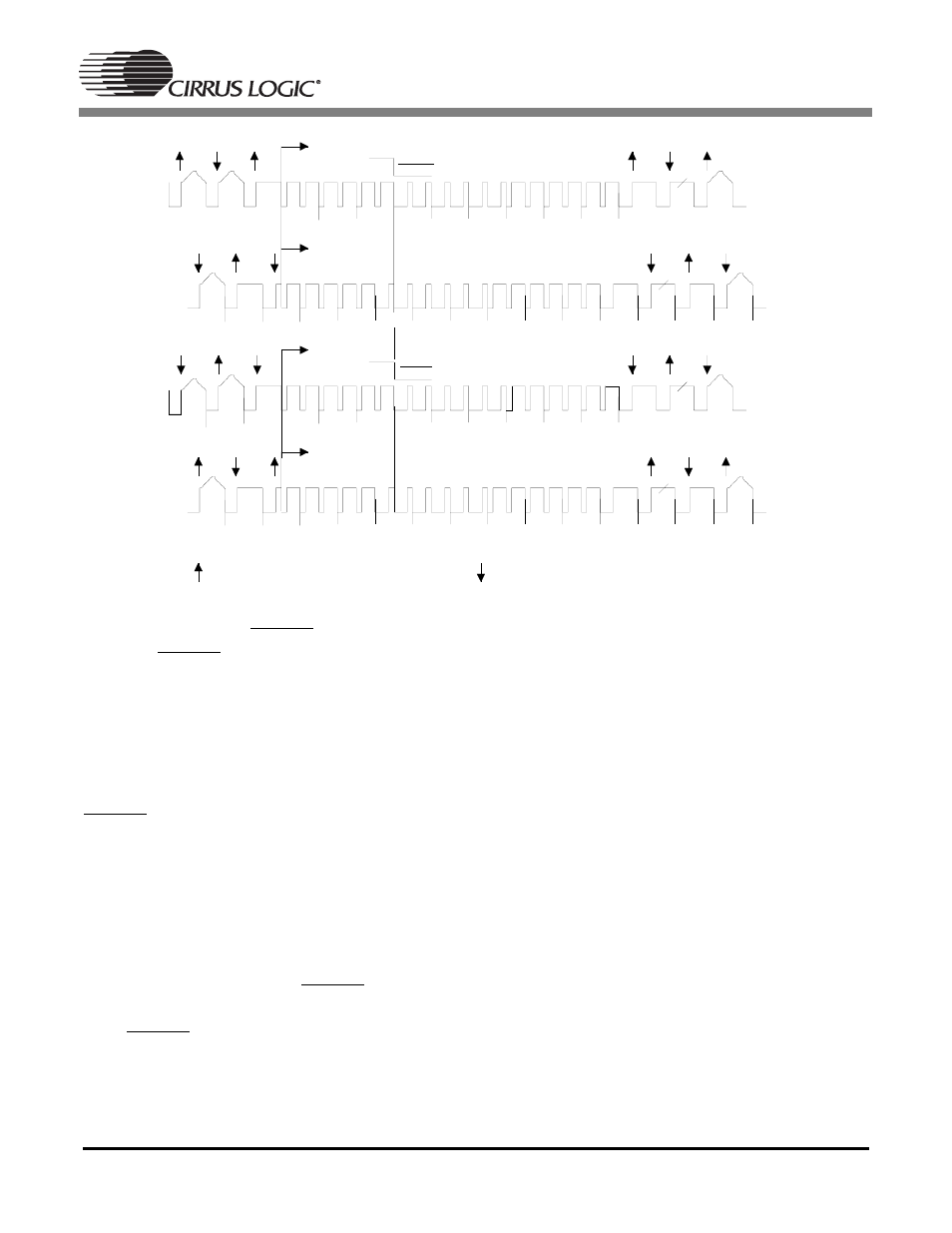

Page 19: Figure 7. ntsc video interlaced timing

CS4954 CS4955

DS278F6

19

Field two begins with VSYNC transitioning low at

line 266. VSYNC stays low for 3 line cycles and

transitions high during the end of line 268. Video

input on the V [7:0] pins is expected between line

284 and line 522. Field two is 263 lines; field one

is 262 lines.

5.2.9 PAL Progressive Scan

VSYNC will transition low at the beginning of the

odd field and will remain low for 2.5 lines or 2160

pixel cycles (864 × 2.5). PAL non-interlaced tim-

ing is illustrated in Figure

. In this mode, the

CS4954/5 expects digital video input on the V [7:0]

pins for 288 lines, beginning on active video line 23

and continuing through line 309.

The second field begins with VSYNC transitioning

low after 312 lines from the beginning of the first

field. VSYNC stays low for 2.5 line-times and tran-

sitions high during the middle of line 315. Video

input on the V [7:0] pins is expected between line

335 through line 622. Field two is 313 lines; field

one is 312 lines.

5.3

ITU-R.BT656

The CS4954/5 supports an ITU-R.BT656 slave

mode feature that is selectable through the ITU-

R.BT656 bit of the CONTROL_0 Register. The

ITU-R.BT656 slave feature is unique because the

horizontal and vertical timing and digital video are

combined into a single 8-bit 27 MHz input. With

ITU-R.BT656 there are no horizontal and vertical

input or output strobes, only 8-bit 27 MHz active

CbYCrY data, with start- and end-of-video codes

implemented using reserved 00 and FF code se-

quences within the video feed. As with all modes,

V [7:0] are sampled with the rising edge of CLK.

The CS4954/5 expects the digital ITU-R.BT656

stream to be error-free. The FIELD

(1)

output tog-

gles as with non ITU-R.BT656 input. ITU-

R.BT656 input timing is illustrated in Figure

523

524

525

1

2

3

4

5

6

7

8

9

VSYNC Drops

10

22

Analog

Field 1

261

262

263

Analog

Field 2

285

284

272

271

270

269

268

267

266

265

264

523

524

525

1

2

3

4

5

6

7

8

9

VSYNC Drops

10

22

Analog

Field 3

261

262

263

Analog

Field 4

285

284

272

271

270

269

268

267

266

265

264

Burst begins with positive half-cycle

Burst begins with negative half-cycle

Figure 7. NTSC Video Interlaced Timing