4 digital video input modes, 5 multi-standard output format modes, Digital video input modes – Cirrus Logic CS4955 User Manual

Page 21: Multi-standard output format modes

CS4954 CS4955

DS278F6

21

5.4

Digital Video Input Modes

The CS4954/5 provides two different digital video

input modes that are selectable through the

IN_MODE bit in the CONTROL_0 Register.

In Mode 0 and upon RESET, the CS4954/5 de-

faults to output a solid color (one of a possible of

256 colors). The background color is selected by

writing the BKG_COLOR Register (0x08). The

colorspace of the register is RGB 3:3:2 and is unaf-

fected by gamma correction. The default color fol-

lowing RESET is blue.

In Mode 1 the CS4954/5 supports a single 8-bit

27 MHz CbYCrY source as input on the V [7:0]

pins. Input video timing can be ITU-R.BT601 mas-

ter or slave or ITU-R.BT656.

5.5

Multi-standard Output Format Modes

The CS4954/5 supports a wide range of output for-

mats compatible with worldwide broadcast stan-

dards. These formats include NTSC-M, NTSC-J,

PAL-B/D/G/H/I, PAL-M, PAL-N, and PAL Com-

bination N (PAL-Nc) which is the broadcast stan-

dard used in Argentina. After RESET, the CS4954/5

defaults to NTSC-M operation with ITU-R.BT601

analog timing. NTSC-J can also be supported in the

Japanese format by turning off the 7.5 IRE pedestal

through the PED bit in the CONTROL_1 Register

(0x01).

Output formats are configured by writing control

registers with the values shown in Table

261

262

1

2

3

4

5

6

7

8

9

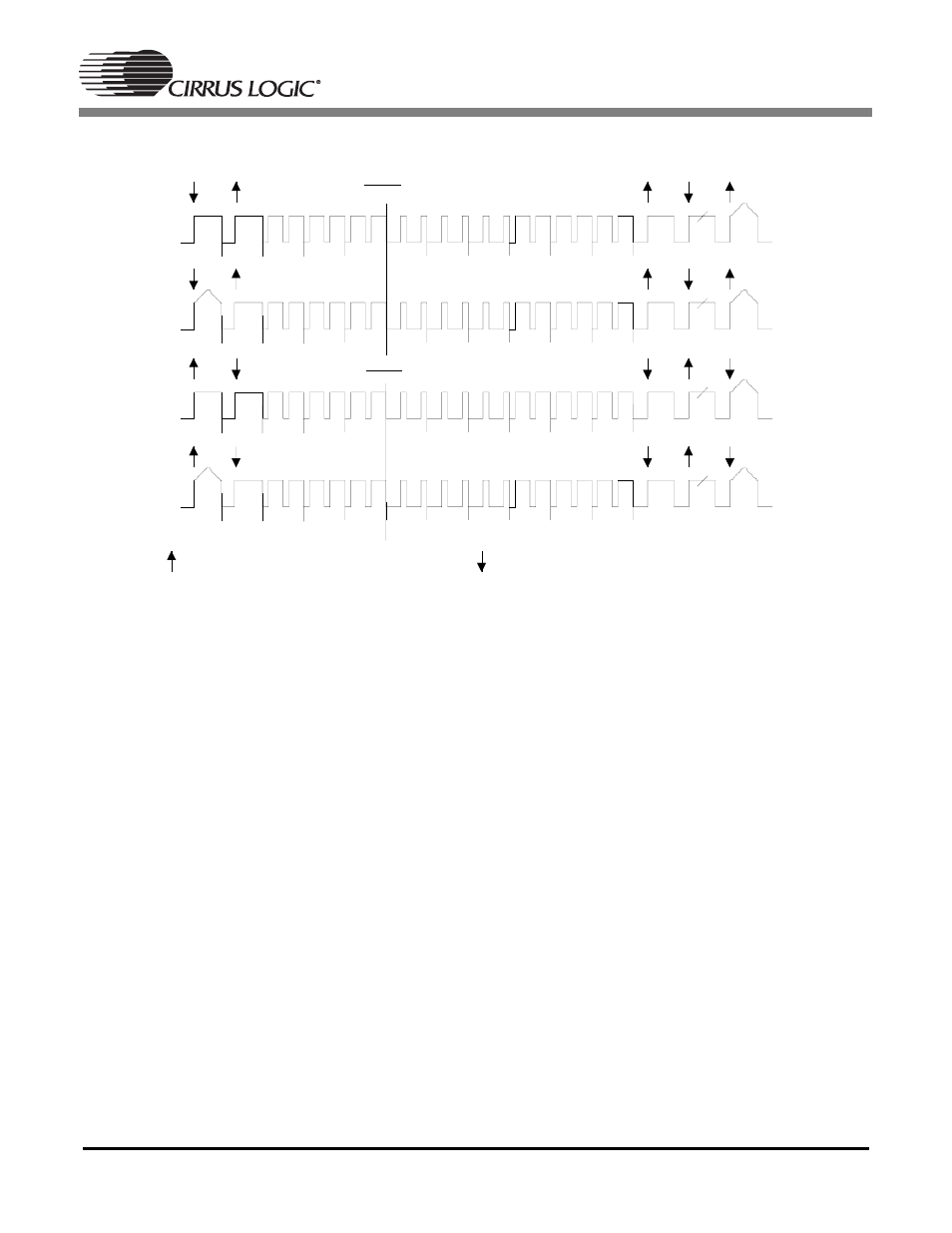

Start of

VSYNC

10

22

Field 1

Burst begins with positive half-cycle

Burst begins with negative half-cycle

Burst phase = reference phase = 180 relative to B-Y

0

Burst phase = reference phase = 180 relative to B-Y

0

262

263

1

2

3

4

5

6

7

8

9

10

22

261

262

1

2

3

4

5

6

7

8

9

10

22

262

263

1

2

3

4

5

6

7

8

9

10

22

Field 2

Field 3

Field 4

Start of

VSYNC

Figure 9. NTSC Video Non-Interlaced Progressive Scan Timing

NOTE 1: The FIELD pin (pin 9) remains an output pin in SLAVE mode. However, the FIELD pin state does not

toggle in SLAVE mode and its output state should be considered random.