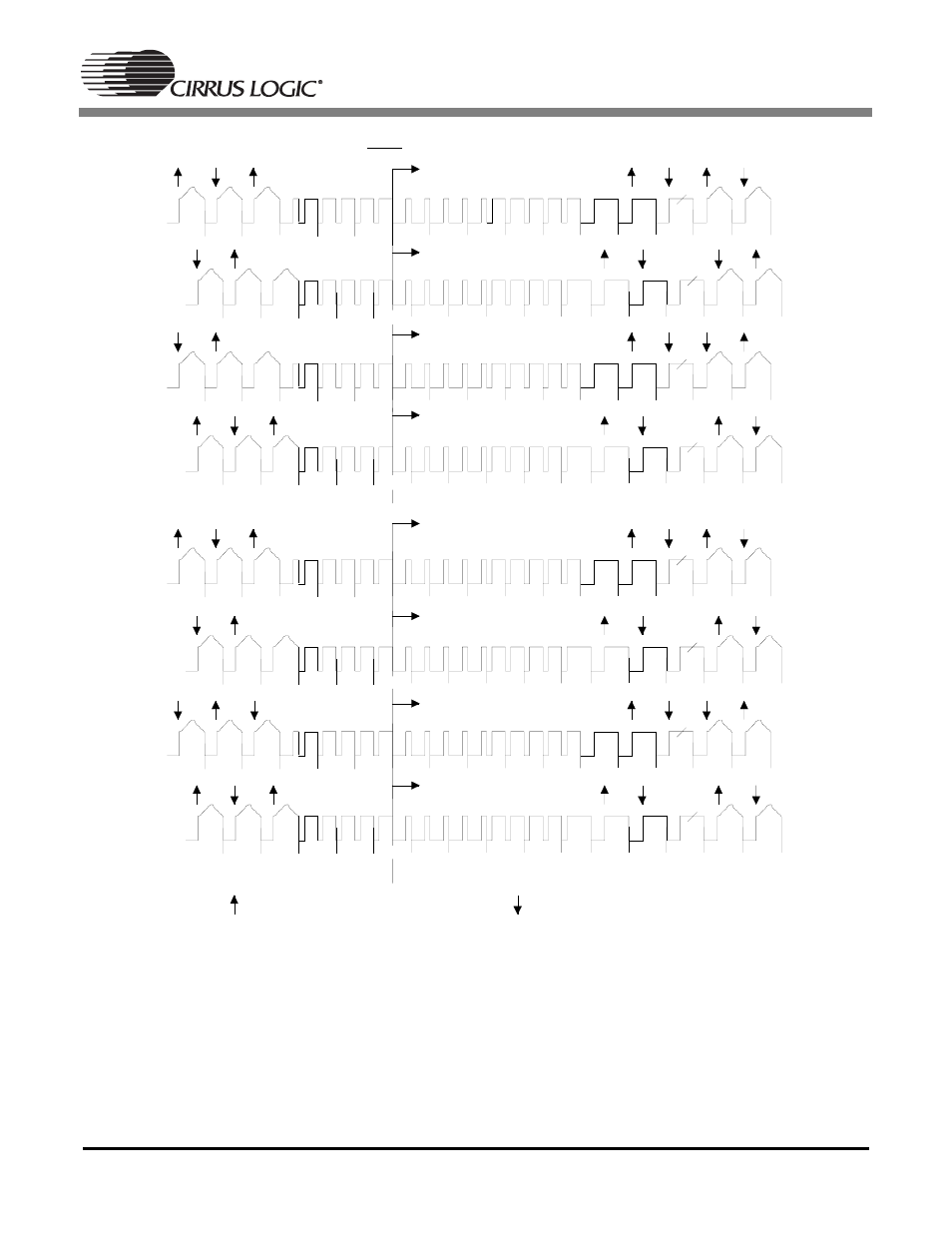

Figure 8. pal video interlaced timing – Cirrus Logic CS4955 User Manual

Page 20

CS4954 CS4955

20

DS278F6

As mentioned above, there are no horizontal and

vertical timing signals necessary in ITU-R.BT656

mode. However in some cases it is advantageous to

output these timing signals for other purposes. By

setting the 656_SYNC_OUT register bit in

CONTROL_6 register, HSYNC and VSYNC are

output,so that other devices in the system can syn-

chronize to these timing signals.

621

622

623

Analog

Field 1

Burst Phase = 135 degrees relative to U

Burst Phase = 225 degrees relative to U

620

624

625

1

2

3

4

5

6

7

23

24

309

310

Analog

Field 2

308

311

312

313

314

315

316

317

318

319

320

336

337

621

622

623

Analog

Field 3

620

624

625

1

2

3

4

5

6

7

23

24

309

310

Analog

Field 4

308

311

312

313

314

315

316

317

318

319

320

336

337

621

622

623

Analog

Field 5

620

624

625

1

2

3

4

5

6

7

23

24

309

310

Analog

Field 6

308

311

312

313

314

315

316

317

318

319

320

336

337

621

622

623

Analog

Field 7

620

624

625

1

2

3

4

5

6

7

23

24

309

310

Analog

Field 8

308

311

312

313

314

315

316

317

318

319

320

336

337

VSYNC Drops

Figure 8. PAL Video Interlaced Timing