Cirrus Logic CS1631 User Manual

Page 49

CS1630/31

DS954F3

49

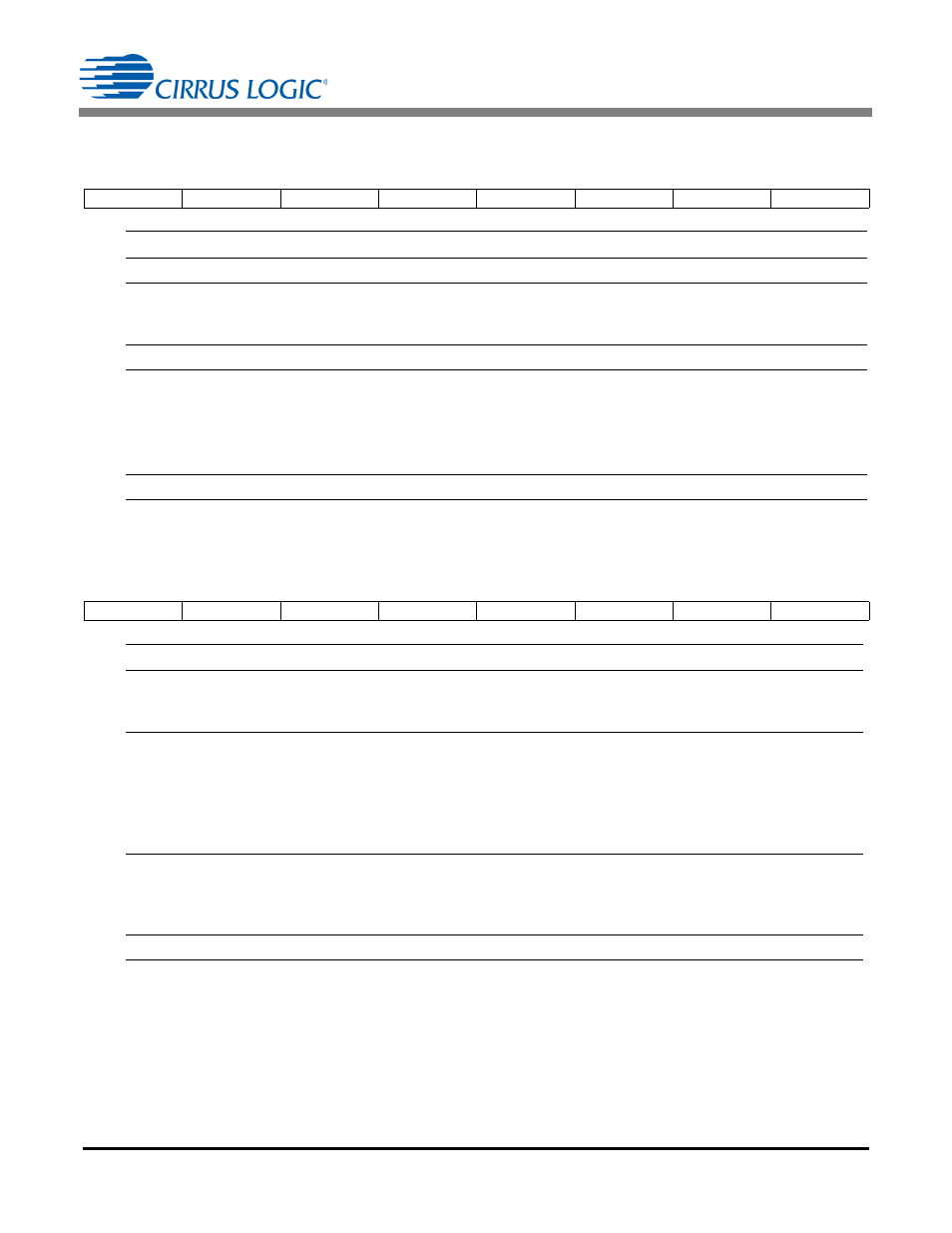

6.41 Configuration 60 (Config60)

–

Address 92

6.42 Configuration 61 (Config61)

–

Address 93

7

6

5

4

3

2

1

0

-

PLC

-

CS_DELAY2

CS_DELAY1

CS_DELAY0

-

-

Number

Name

Description

[7]

-

Reserved

[6]

PLC

Configures the power line calibration (PLC) mode.

0 = Enable

1 = Disable

[5]

-

Reserved

[4:2]

CS_DELAY[2:0]

Configures the I

Sense

comparator delay and board delays incurred through

FET switching T1

comp

. Switching time T1

comp

can be set from 0ns to 350ns in

steps of 50ns.

[1:0]

-

Reserved

7

6

5

4

3

2

1

0

DITNODIM

DITLEVEL1

DITLEVEL0

DITCHAN

-

-

-

-

Number

Name

Description

[7]

DITNODIM

Configures dithering, if enabled, to work in No-dimmer mode only.

0 = Dithering works in all modes

1 = Dithering works in No-dimmer mode only

[6:5]

DITLEVEL[1:0]

Configures the second stage dithering level based on the percentage of varia-

tion on the I

Sense

DAC reference setting.

00 = 1.3%

01 = 2.9%

10 = 6%

11 = 12.3%

[4]

DITCHAN

Selects the channel for less dithering for which the nominal dither level, set

using bits DITLEVEL[1:0], is attenuated by the amount set by bits DITATT[1:0].

0 = Channel 1

1 = Channel 2

[3:0]

-

Reserved

T1

comp

CS_DELAY[2:0] 50ns

=