Cirrus Logic CS1631 User Manual

Page 35

CS1630/31

DS954F3

35

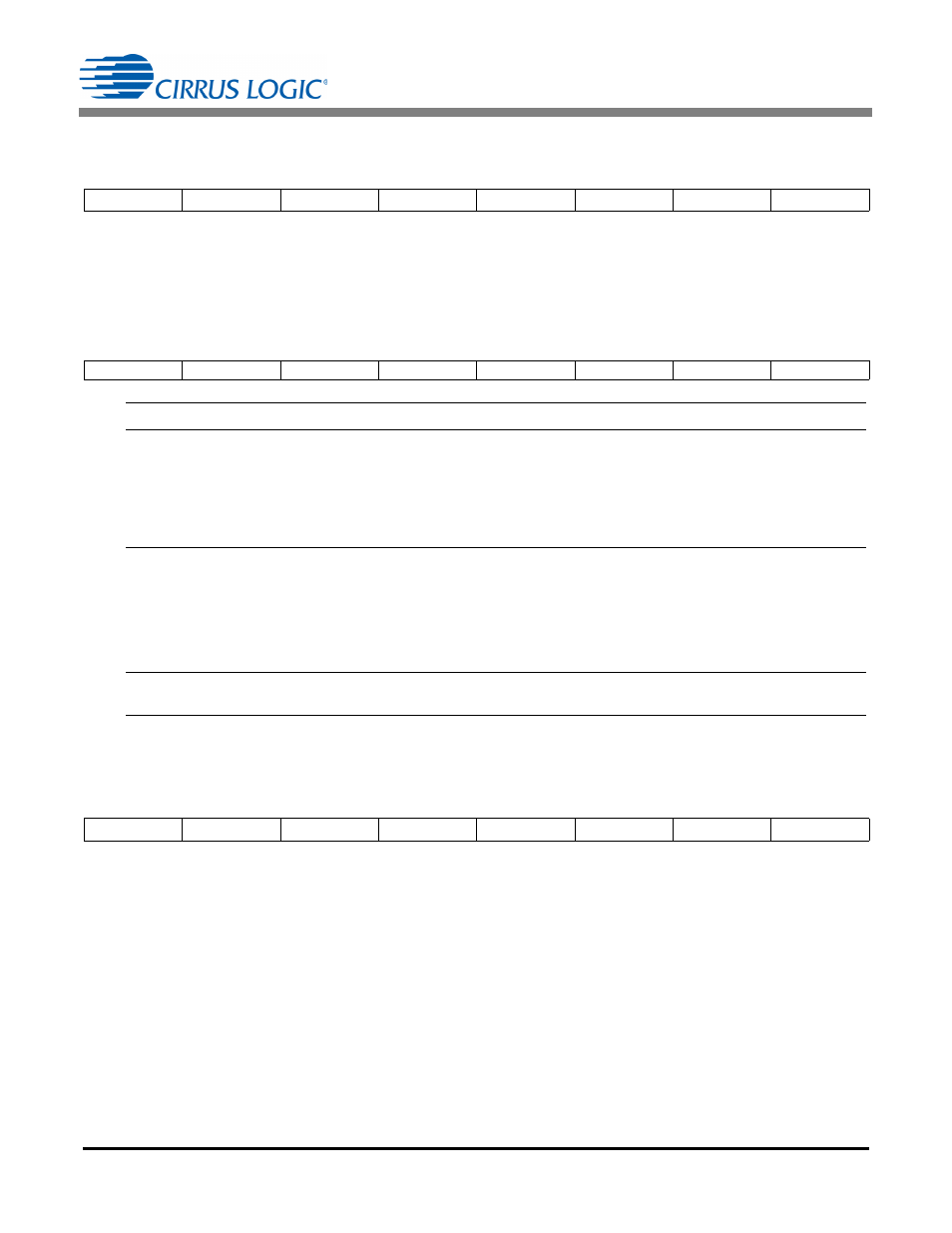

6.14 Channel 1 Output Current (CH1CUR)

–

Address 41

CH1CUR sets the target output current for channel 1. The register value plus bit CH1CURMSB forms an un-

signed integer in the range of 0

value511.

6.15 Configuration 10 (Config10)

–

Address 42

6.16 Channel 2 Output Current (CH2CUR)

–

Address 43

CH2CUR sets the target output current for channel 2. The register value plus bit CH2CURMSB forms an un-

signed integer in the range of 0

value511.

7

6

5

4

3

2

1

0

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

0

7

6

5

4

3

2

1

0

BUCK3

BUCK2

BUCK1

BUCK0

RE1_ZCD2

RE1_ZCD1

RE1_ZCD0

CH2CURMSB

Number

Name

Description

[7:4]

BUCK[3:0]

Configures buck topology. The value is an unsigned integer in the range of

0

value15.

0 = Normal buck configuration

1 = Tapped buck ratio of one which is equivalent to a normal buck

configuration

2-15 = Tapped buck configuration where the ratio is equal to N.

[3:1]

RE1_ZCD[2:0]

Configures fixed time delay T

RE1ZCD(delay)

for zero-current detection (ZCD)

comparator to account for the delay on the rising edge of ZCD for channel 1.

The value is an unsigned integer in the range of 0

value7. The delay is

defined by:

[0]

CH2CURMSB

Most significant bit for the CH2CUR register (see "Channel 2 Output Current

(CH2CUR) – Address 43" on page 35).

7

6

5

4

3

2

1

0

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

0

T

RE1ZCD delay

RE1_ZCD

=

[2:0] 50ns