2 persistence, 3 watch dog, 2 persistence 5.3 watch dog – Cirrus Logic CobraNet User Manual

Page 26

26

©

Copyright 2006 Cirrus Logic, Inc.

DS651PM25

CobraNet Programmer’s Reference

Management Interface

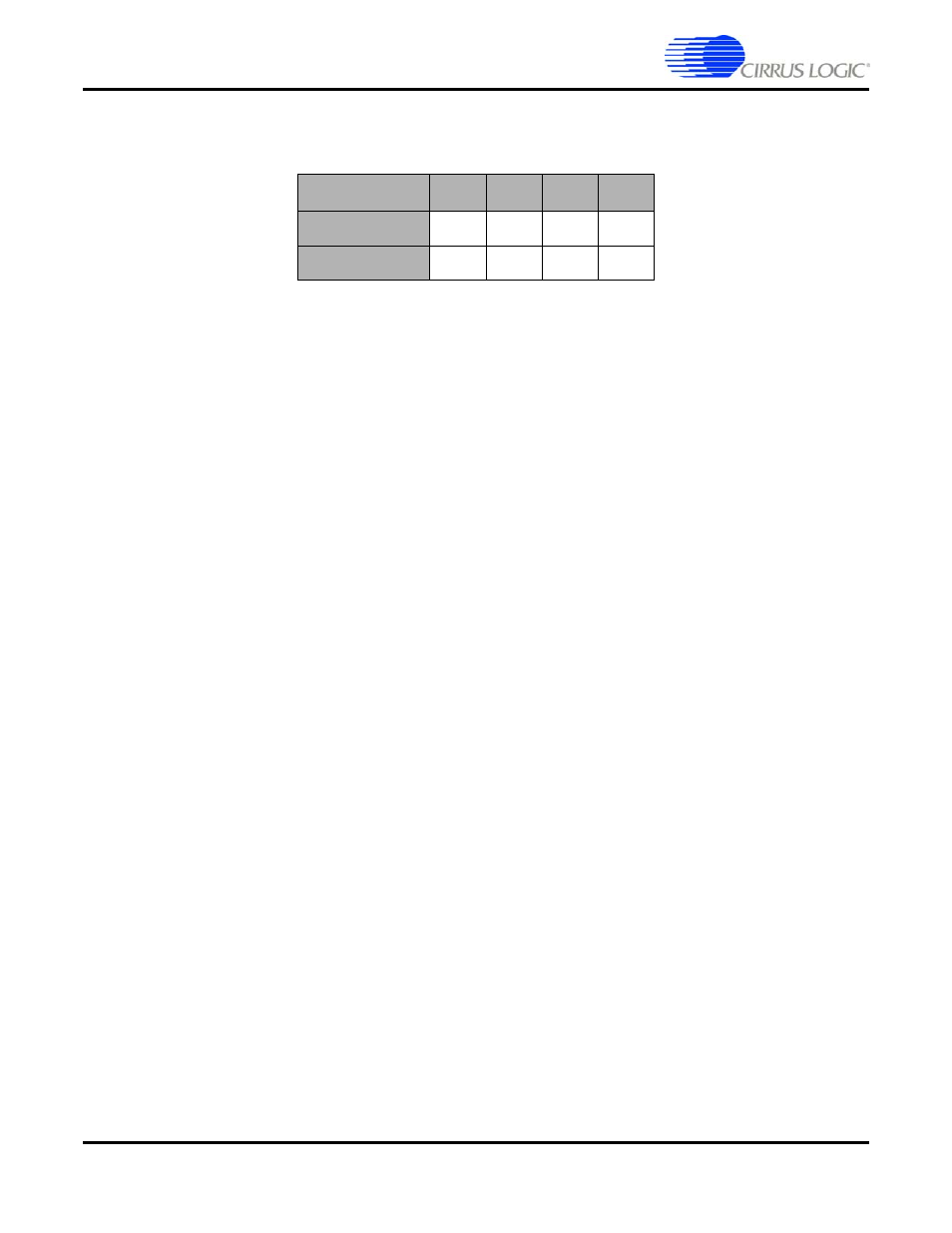

On 32-bit CobraNet platforms, the transmit buffer is comprised of 4-byte words. The

mapping between the byte-wide flash data and the wider buffer memory is as follows.

5.2

Persistence

The persistence feature causes values written to Read/write-persistent type variables to

be written to flash and for these stored values to be restored during startup. With the

persistence feature disabled, Read/write and Read/write-persistent variables behave

identically. Persistence is enabled by setting the

flashPersistEnable variable.

With persistence enabled, values written to Read/write-persistent variables are written to

flash by a background task according to a schedule designed to prevent excessive write

cycles on the memory and to avoid interference with other critical functions. In extreme

cases it can take up to 1 minute to store changed values. However, the persistence

feature is implemented such that it is safe to remove power at any time with the caveat

that the values recalled may not include changes made immediately prior to removal of

power. Variable values will never become corrupted due to unexpected loss of power or

network connection.

flashPersistAck can be used to ensure that variables have been stored to non-volatile

memory prior to removal of power.

5.3

Watch Dog

The watch dog is a digital signal from the CobraNet interface provided to allow fault

detection. The watch dog signal is toggled periodically by firmware to indicate normal

operation. The toggle rate may drop to as low as 5 Hz on occasion, depending on

processor load. Actual minimum, maximum, and nominal toggle rates can be found in the

Hardware Reference Manual applicable to the particular CobraNet interface.The watch

dog signal will stop toggling following detection and reporting of a fatal error condition.

The interface should be reset and re-initialized when absence of the watchdog signal is

detected.

Use of the watchdog requires external hardware and/or software. A hardware solution

may be implemented with a “microprocessor manager” chip such as the DS1236 from

Dallas/Maxim. A software solution could involve wiring the watch dog signal to an I/O port,

timer, or interrupt on the host processor and then wiring the CobraNet reset signal to a

general purpose output. Software on the host processor would monitor the interval

between watch dog transitions and assert the reset signal if the interval exceeds the

maximum period.

Implementation of the watch dog feature is not mandatory but is recommended. ESD,

EMI, and power fluctuation events are not uncommon in audio installations and the ability

to survive and recover from such conditions is a prerequisite for passing many electrical

certification programs.

Table 9. Flash Layout, 32-bit Platforms

MS

MH

ML

LS

First Word

Byte 4

Byte 3

Byte 2

Byte 1

Second Word

Byte 8

Byte 7

Byte 6

Byte 5