2 wiring, 3internal circuit schematic – Horner APG SmartStack I/O HE-ADC920* User Manual

Page 2

PAGE 2

10 NOV 2006

MAN0317-09

ADC920

Information is subject to change without notice. SmartStack is a trademark of Horner APG, LLC.

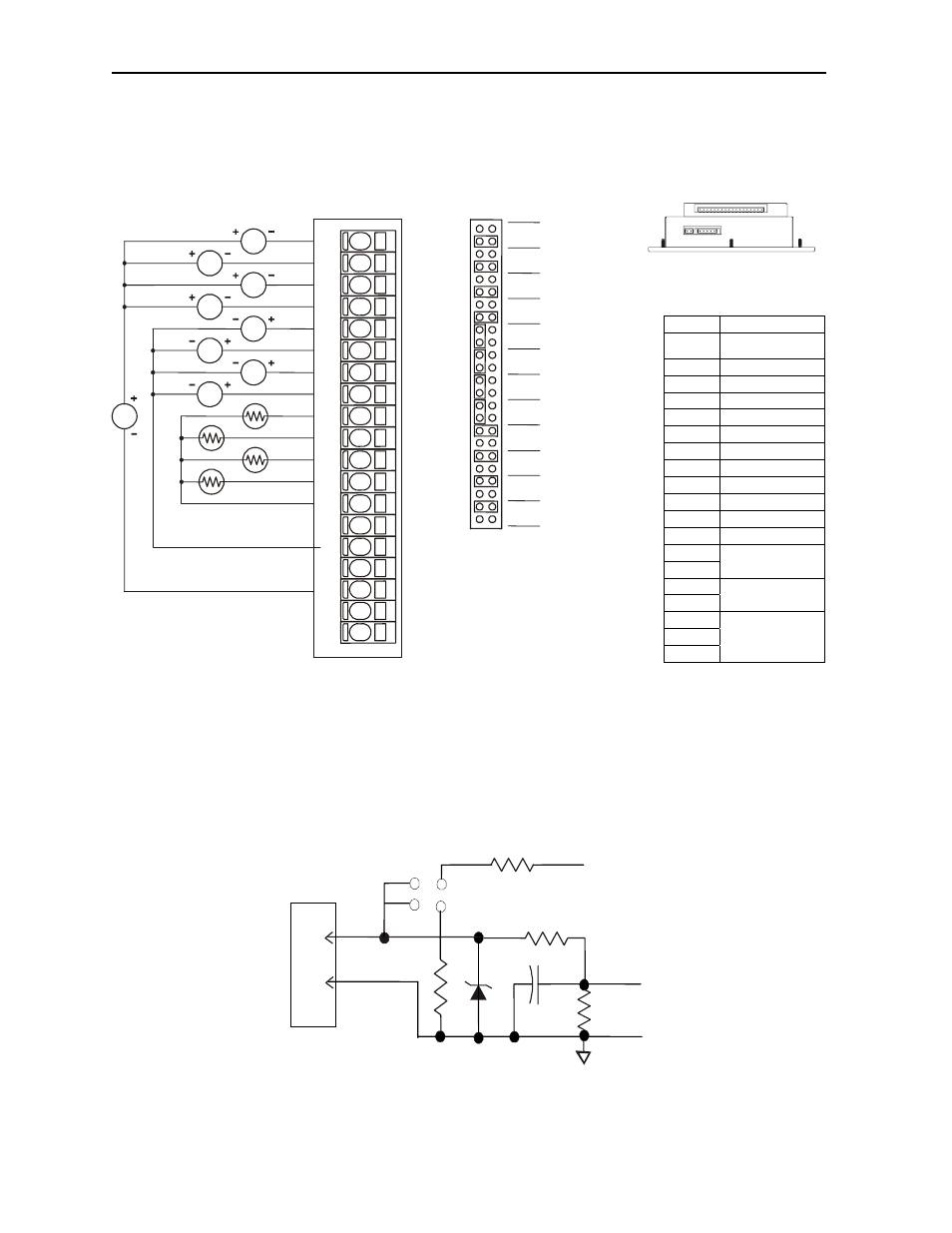

2 WIRING

3

INTERNAL CIRCUIT SCHEMATIC

*

OCS Bottom View – Shows

Corresponding I/O Pin

Pin

ADC920

I1

*

Input 1

I2 Input

2

I3 Input

3

I4 Input

4

I5 Input

5

I6 Input

6

I7 Input

7

I8 Input

8

I9 Input

9

I10 Input

10

I11 Input

11

I12 Input

12

C1

C1

Thermistor

Common

C2

C2

0 – 5VDC

Common

C3

C3

C3

20mA

Common

The jumper block indicates the

correct jumper positions for the

wiring shown.

For more information, refer to

Section 4.2 (b), Hardware

Configuration in this document.

I/O Connector

To

Controller

250Ω

1+

Com

V Ref

10K

Ω

SmartStack

Field

Side

CH 2

CH 12

CH 1

CH 3

CH 4

CH 5

CH 6

CH 7

CH 8

CH 9

CH 10

CH 11

V

I1

I2

I3

I4

I10

I11

I12

C1

I5

I6

I7

I8

C1

C2

C2

C3

I9

T

T

T

T

C3

001ADC003-R2

20

ma

20

ma

20

ma

5 V

20

ma

5 V

5 V

5 V

C3

*