Output enable time, Capacitive loading, Adsp-ts201s – Analog Devices TigerSHARC ADSP-TS201S User Manual

Page 38: And the drive current, i, Is the difference between t, And t, As shown in figure 35 . the t ime t, Is calculated with test load c, Drive current i, And with δv equal to 0.4 v

Rev. C

|

Page 38 of 48

|

December 2006

ADSP-TS201S

Output Enable Time

Output pins are considered to be enabled when they have made

a transition from a high impedance state to when they start driv-

ing. The time for the voltage on the bus to ramp by

ΔV is

dependent on the capacitive load, C

L

, and the drive current, I

D

.

This ramp time can be approximated by the following equation:

The output enable time t

ENA

is the difference between

t

MEASURED_ENA

and t

RAMP

as shown in

. The time

t

MEASURED_ENA

is the interval from when the reference signal

switches to when the output voltage ramps

ΔV from the mea-

sured three-stated output level. t

RAMP

is calculated with test load

C

L

, drive current I

D

, and with

ΔV equal to 0.4 V.

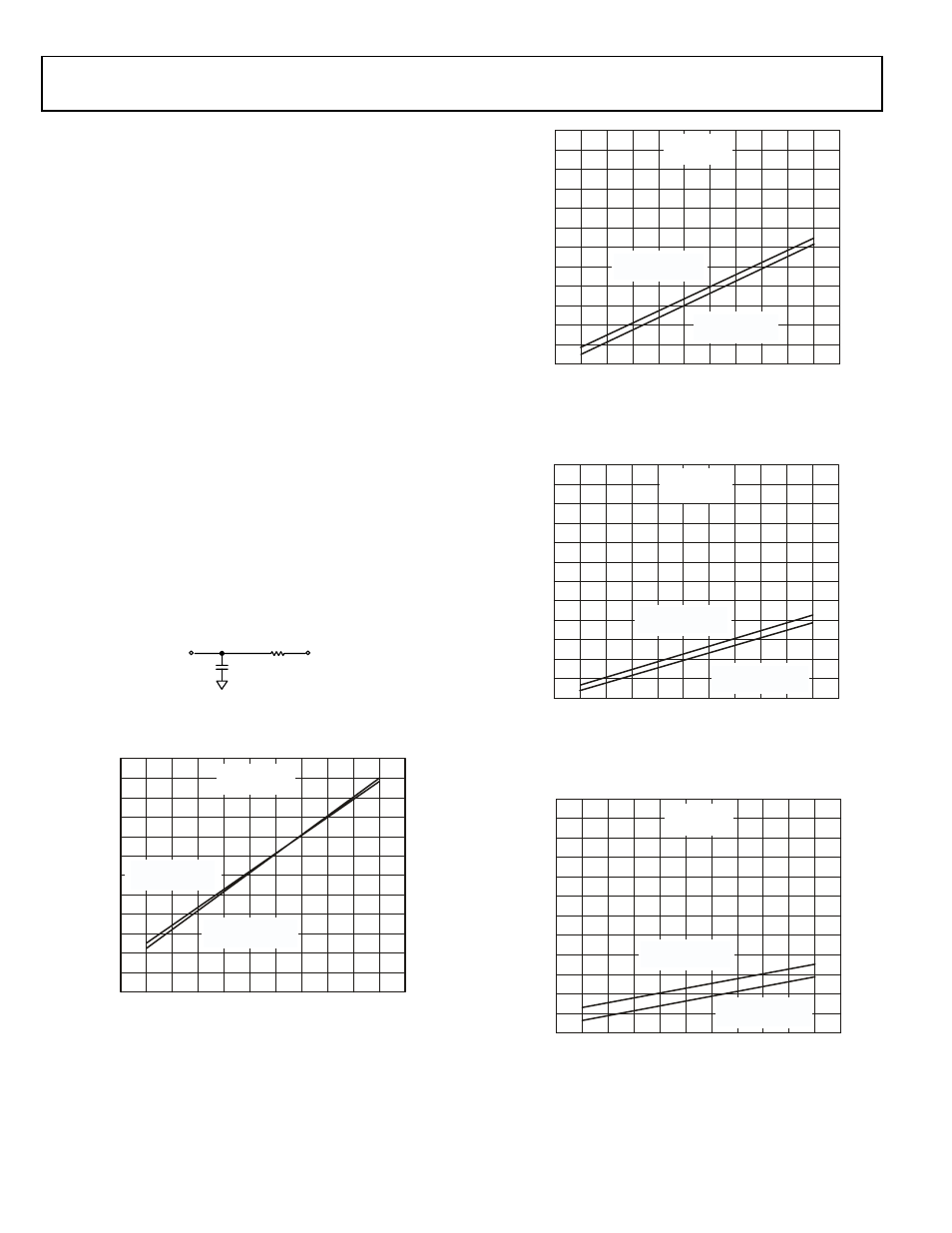

Capacitive Loading

Output valid and hold are based on standard capacitive loads:

30 pF on all pins (see

). The delay and hold specifica-

tions given should be derated by a drive strength related factor

for loads other than the nominal value of 30 pF.

through

show how output rise time varies with capac-

itance.

graphically shows how output valid varies with

load capacitance. (Note that this graph or derating does not

apply to output disable delays; see

.) The graphs of

through

may not be

linear outside the ranges shown.

Figure 36. Equivalent Device Loading for AC Measurements

(Includes All Fixtures)

Figure 37. Typical Output Rise and Fall Time (10% to 90%, V

DD_IO

= 2.5 V)

vs. Load Capacitance at Strength 0

t

RAMP

C

L

V

Δ

(

) I

D

⁄

=

1.25V

TO

OUTPUT

PIN

30pF

50

⍀

0

10

20

30

40

50

60

70

80

90

100

0

5

10

15

20

25

RISE TIME

Y = 0.259x + 3.0842

STRENGTH 0

(V

DD_IO

= 2.5V)

R

IS

E

A

N

D

F

A

L

L

T

IM

E

S

(n

s

)

LOAD CAPACITANCE (pF)

FALL TIME

Y = 0.251x + 4.2245

Figure 38. Typical Output Rise and Fall Time (10% to 90%, V

DD_IO

= 2.5 V)

vs. Load Capacitance at Strength 1

Figure 39. Typical Output Rise and Fall Time (10% to 90%, V

DD_IO

= 2.5 V)

vs. Load Capacitance at Strength 2

Figure 40. Typical Output Rise and Fall Time (10% to 90%, V

DD_IO

= 2.5 V)

vs. Load Capacitance at Strength 3

0

10

20

30

40

50

60

70

80

90

100

0

5

10

15

20

25

R

IS

E

A

N

D

F

A

L

L

T

IM

E

S

(n

s

)

LOAD CAPACITANCE (pF)

STRENGTH 1

(V

DD_IO

= 2.5V)

RISE TIME

Y = 0.1501

x + 0.05

FALL TIME

Y = 0.1527x + 0.7485

0

10

20

30

40

50

60

70

80

90

100

0

5

10

15

20

25

R

IS

E

A

N

D

F

A

L

L

T

IM

E

S

(n

s

)

LOAD CAPACITANCE (pF)

STRENGTH 2

(V

DD_IO

= 2.5V)

RISE TIME

Y = 0.0861

x + 0.4712

FALL TIME

Y = 0.0949x + 0.8112

0

10

20

30

40

50

60

70

80

90

100

0

5

10

15

20

25

R

IS

E

A

N

D

F

A

L

L

T

IM

E

S

(n

s

)

LOAD CAPACITANCE (pF)

STRENGTH 3

(V

DD_IO

= 2.5V)

RISE TIME

Y = 0.06

x + 1.1362

FALL TIME

Y = 0.0691x + 1.1158