Strap pin function descriptions, Adsp-ts201s – Analog Devices TigerSHARC ADSP-TS201S User Manual

Page 20

Rev. C

|

Page 20 of 48

|

December 2006

ADSP-TS201S

STRAP PIN FUNCTION DESCRIPTIONS

Some pins have alternate functions at reset. Strap options set

DSP operating modes. During reset, the DSP samples the strap

option pins. Strap pins have an internal pull-up or pull-down

for the default value. If a strap pin is not connected to an over-

driving external pull-up, pull-down, or logic load, the DSP

samples the default value during reset. If strap pins are

connected to logic inputs, a stronger external pull-up or pull-

down may be required to ensure default value depending on

leakage and/or low level input current of the logic load. To set a

mode other than the default mode, connect the strap pin to a

sufficiently stronger external pull-up or pull-down.

lists and describes each of the DSP’s strap pins.

When default configuration is used, no external resistor is

needed on the strap pins. To apply other configurations, a

500

Ω resistor connected to V

DD_IO

is required. If providing

external pull-downs, do not strap these pins directly to V

SS

; the

strap pins require 500

Ω resistor straps.

All strap pins are sampled on the rising edge of RST_IN (deas-

sertion edge). Each pin latches the strapped pin state (state of

the strap pin at the rising edge of RST_IN). Shortly after deas-

sertion of RST_IN, these pins are reconfigured to their normal

functionality.

These strap pins have an internal pull-down resistor, pull-up

resistor, or no-resistor (three-state) on each pin. The resistor

type, which is connected to the I/O pad, depends on whether

RST_IN is active (low) or if RST_IN is deasserted (high).

shows the resistors that are enabled during active reset

and during normal operation.

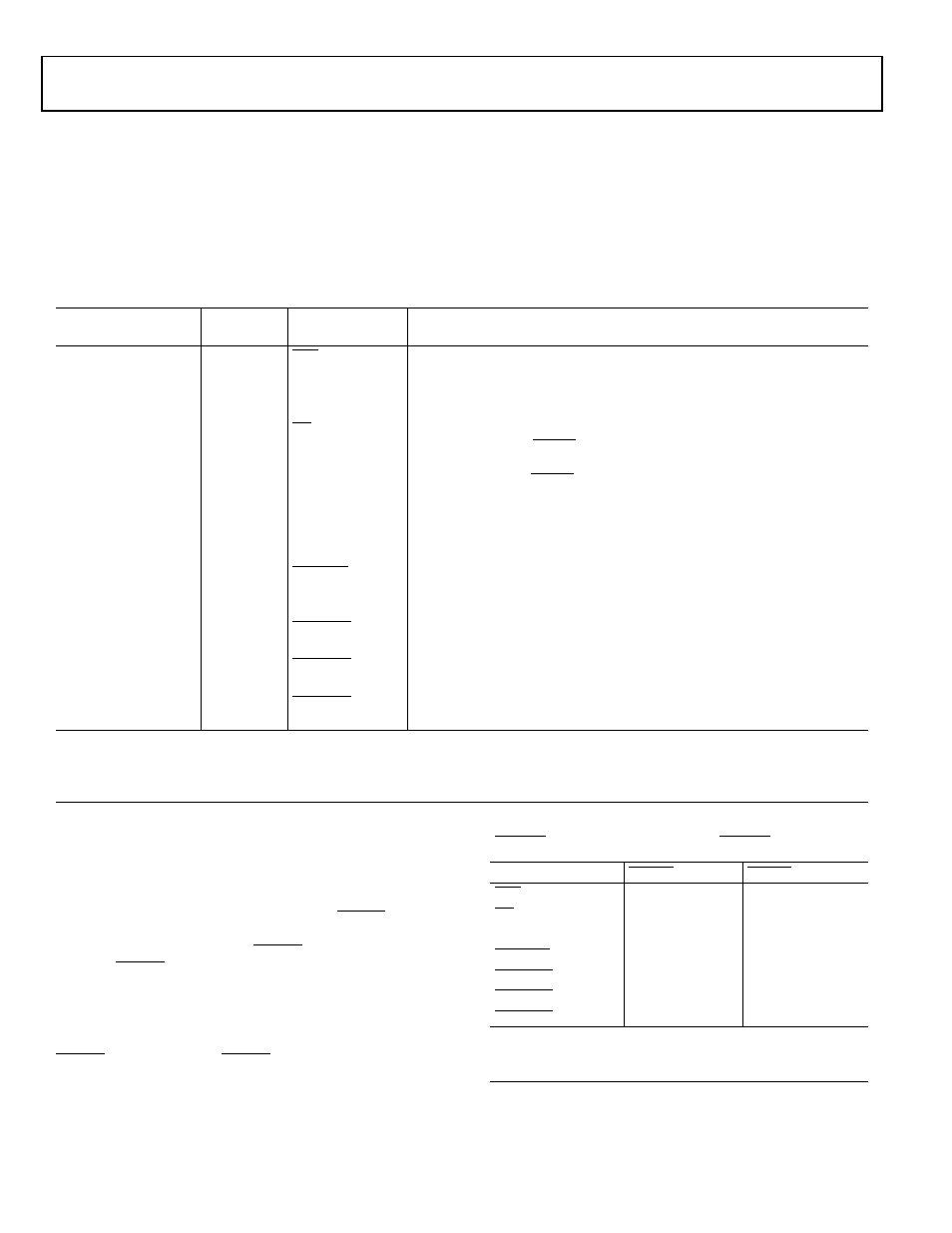

Table 16. Pin Definitions—I/O Strap Pins

Signal

Type (at

Reset)

On Pin …

Description

EBOOT

I

(pd_0)

BMS

EPROM Boot.

0 = boot from EPROM immediately after reset (default)

1 = idle after reset and wait for an external device to boot DSP

through the external port or a link port

IRQEN

I

(pd)

BM

Interrupt Enable.

0 = disable and set IRQ3–0 interrupts to edge-sensitive after

reset (default)

1 = enable and set IRQ3–0 interrupts to level-sensitive

immediately after reset

LINK_DWIDTH

I

(pd)

TMR0E

Link Port Input Default Data Width.

0 = 1-bit (default)

1 = 4-bit

SYS_REG_WE

I

(pd_0)

BUSLOCK

SYSCON and SDRCON Write Enable.

0 = one-time writable after reset (default)

1 = always writable

TM1

I

(pu)

L1BCMPO

Test Mode 1. Do not overdrive default value during reset.

TM2

I

(pu)

L2BCMPO

Test Mode 2. Do not overdrive default value during reset.

TM3

I

(pu)

L3BCMPO

Test Mode 3. Do not overdrive default value during reset.

I = input; A = asynchronous; O = output; OD = open-drain output; T = three-state; P = power supply; G = ground; pd = internal pull-down

5 k

Ω

; pu = internal pull-up 5 k

Ω

; pd_0 = internal pull-down 5 k

Ω

on DSP ID = 0; pu_0 = internal pull-up 5 k

Ω

on DSP ID = 0; pu_od_0 = internal

pull-up 500

Ω

on DSP ID = 0; pd_m = internal pull-down 5 k

Ω

on DSP bus master; pu_m = internal pull-up 5 k

Ω

on DSP bus master; pu_ad

= internal pull-up 40 k

Ω

. For more pull-down and pull-up information, see

Electrical Characteristics on Page 22

Table 17. Strap Pin Internal Resistors—Active Reset

(RST_IN = 0) vs. Normal Operation (RST_IN = 1)

Pin

RST_IN = 0

RST_IN = 1

BMS

(pd_0)

(pu_0)

BM

(pd)

Driven

TMR0E

(pd)

Driven

BUSLOCK

(pd_0)

(pu_0)

L1BCMPO

(pu)

Driven

L2BCMPO

(pu)

Driven

L3BCMPO

(pu)

Driven

pd = internal pull-down 5 k

Ω

; pu = internal pull-up 5 k

Ω

;

pd_0 = internal pull-down 5 k

Ω

on DSP ID = 0;

pu_0 = internal pull-up 5 k

Ω

on DSP ID = 0