Adsp-ts201s-specifications, Operating conditions, Adsp-ts201s—specifications – Analog Devices TigerSHARC ADSP-TS201S User Manual

Page 21: Adsp-ts201s

ADSP-TS201S

Rev. C

|

Page 21 of 48

|

December 2006

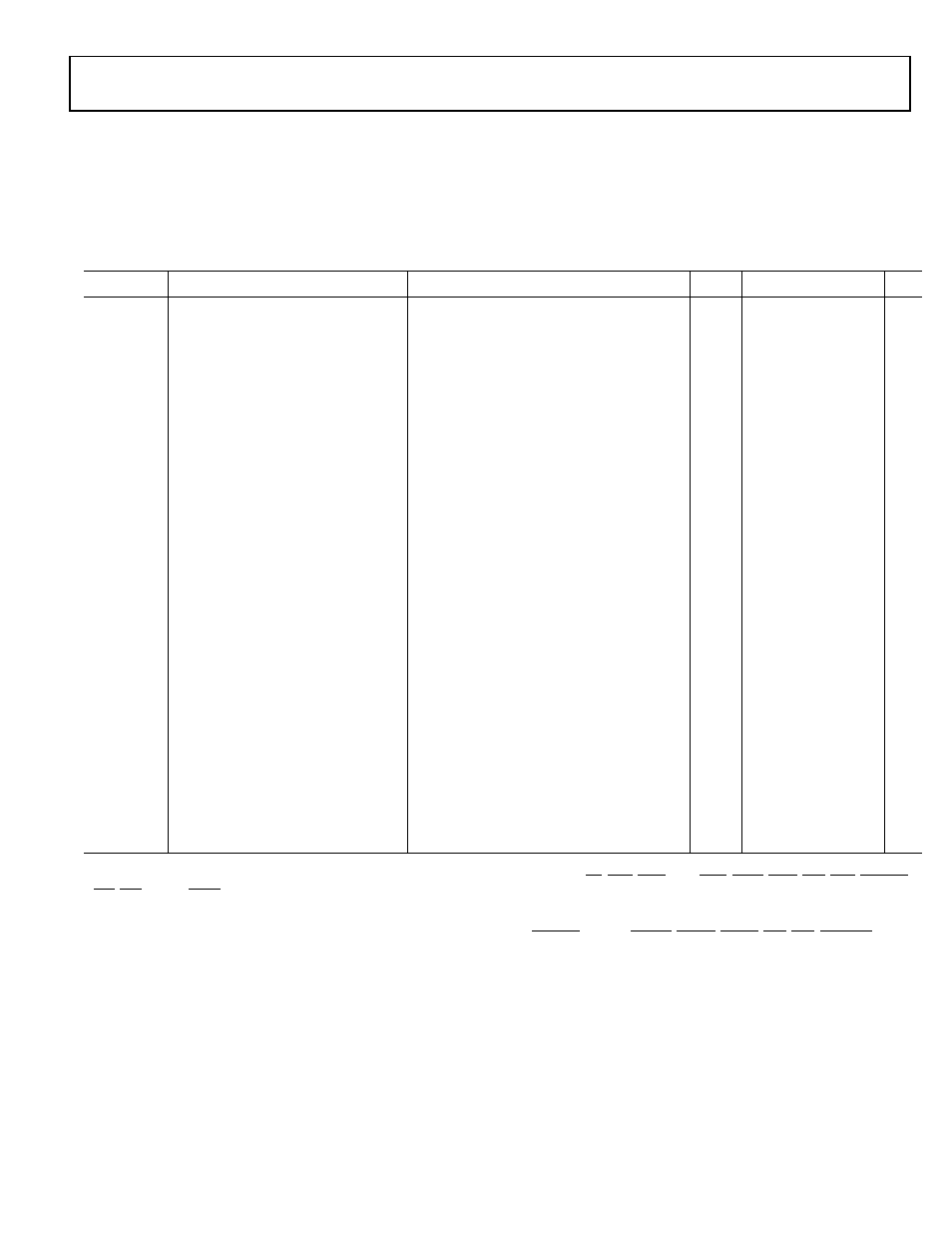

ADSP-TS201S—SPECIFICATIONS

Note that component specifications are subject to change with-

out notice. For information on link port electrical

characteristics, see

Link Port Low Voltage, Differential-Signal

(LVDS) Electrical Characteristics, and Timing on Page 30

.

OPERATING CONDITIONS

Parameter

Description

Test Conditions

Grade

1

1

Specifications vary for different grades (for example, SABP-060, SABP-050, SWBP-050). For more information on part grades, see

Min

Typ

Max

Unit

V

DD

Internal Supply Voltage

@ CCLK = 600 MHz

060

1.14

1.20

1.26

V

@ CCLK = 500 MHz

050

1.00

1.05

1.10

V

V

DD_A

Analog Supply Voltage

@ CCLK = 600 MHz

060

1.14

1.20

1.26

V

@ CCLK = 500 MHz

050

1.00

1.05

1.10

V

V

DD_IO

I/O Supply Voltage

(all)

2.38

2.50

2.63

V

V

DD_DRAM

Internal DRAM Supply Voltage

@ CCLK = 600 MHz

060

1.52

1.60

1.68

V

@ CCLK = 500 MHz

050

1.425

1.500

1.575

V

T

CASE

Case Operating Temperature

A

–40

+85

°C

T

CASE

Case Operating Temperature

W

–40

+105

°C

V

IH1

High Level Input Voltage

2,

3

2

V

IH1

specification applies to input and bidirectional pins: SCLKRAT2–0, SCLK, ADDR31–0, DATA63–0, RD, WRL, WRH, ACK, BRST, BR7–0, BOFF, HBR, HBG, MSSD3–0,

RAS, CAS, SDCKE, SDWE, TCK, FLAG3–0, DS2–0, ENEDREG.

3

Values represent dc case. During transitions, the inputs may overshoot or undershoot to the voltage shown in

, based on the transient duty cycle. The dc case is equivalent

to 100% duty cycle.

@ V

DD

, V

DD_IO

= Max

(all)

1.7

3.63

V

V

IH2

High Level Input Voltage

3,

4

4

V

IH2

specification applies to input and bidirectional pins: TDI, TMS, TRST, CIMP1–0, ID2–0, LxBCMPI, LxACKI, POR_IN, RST_IN, IRQ3–0, CPA, DPA, DMAR3–0.

@ V

DD

, V

DD_IO

= Max

(all)

1.9

3.63

V

V

IL

Low Level Input Voltage

3,

5

5

Applies to input and bidirectional pins.

@ V

DD

, V

DD_IO

= Min

(all)

–0.33

+0.8

V

I

DD

V

DD

Supply Current, Typical Activity

6

6

For details on internal and external power calculation issues, including other operating conditions, see the EE-170, Estimating Power for the ADSP-TS201S on the Analog Devices

website.

@ CCLK = 600 MHz, V

DD

= 1.20 V, T

CASE

= 25°C

060

2.90

A

@ CCLK = 500 MHz, V

DD

= 1.05 V, T

CASE

= 25°C

050

2.06

A

I

DD_A

V

DD_A

Supply Current, Typical Activity

@ CCLK = 600 MHz, V

DD

= 1.20 V, T

CASE

= 25°C

060

25

55

mA

@ CCLK = 500 MHz, V

DD

= 1.05 V, T

CASE

= 25°C

050

20

50

mA

I

DD_IO

V

DD_IO

Supply Current, Typical Activity

6

@ SCLK = 62.5 MHz, V

DD_IO

= 2.5 V, T

CASE

= 25°C

(all)

0.15

A

I

DD_DRAM

V

DD_DRAM

Supply Current, Typical Activity

6

@ CCLK = 600 MHz, V

DD_DRAM

= 1.6 V, T

CASE

= 25°C 060

0.28

0.43

A

@ CCLK = 500 MHz, V

DD_DRAM

= 1.5 V, T

CASE

= 25°C 050

0.25

0.40

A

V

REF

Voltage Reference

(all)

(V

DD_IO

×0.56)±5%

V

SCLK_V

REF

Voltage Reference

(all)

(V

CLOCK

_

DRIVE

× 0.56) ±5%

V