Typical operating characteristics, Electrical characteristics (continued) – Rainbow Electronics MAX3634 User Manual

Page 3

MAX3634

622Mbps/1244Mbps Burst-Mode Clock Phase

Aligner for GPON OLT Applications

_______________________________________________________________________________________

3

ELECTRICAL CHARACTERISTICS (continued)

(V

CC

= +3.0V to +3.6V, T

A

= -40

°C to +85°C. Typical values are at V

CC

= +3.3V, T

A

= +25

°C, unless otherwise noted.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

622Mbps (Notes 1, 2)

500

Serial Data Output Clock-to-Q

Delay (Figure 1)

t

CLK-Q

1244Mbps (Notes 1, 2)

250

ps

622Mbps (Notes 1, 2)

500

Serial Data Output Q-to-Clock

Delay (Figure 1)

t

Q-CLK

1244Mbps (Notes 1, 2)

250

ps

RATESEL Input High

V

IH

2

V

RATESEL Input Low

V

IL

0.8

V

RATESEL Input Current

V

IN

= 0V or V

CC

-100

+100

µA

Note 1: PECL output must have external termination of 50

Ω to V

CC

- 2V (Thevenin equivalent).

Note 2: AC parameters are guaranteed by design and characterization.

Note 3: From start of PON burst, 101010101010 preamble sequence.

Note 4: BER, acquisition time requirements are met with 100mV

P-P

sinusoidal noise on V

CC

, 0 < f

NOISE

≤ 10MHz.

Note 5: Measured with 20ps

RMS

input random jitter (1.244Mbps), 30ps

RMS

(622Mbps)

Note 6: Jitter tolerance refers to the variation in phase between REFCLK and SDI after acquisition.

Typical Operating Characteristics

(V

CC

= +3.3V and T

A

= +25

°C, unless otherwise noted)

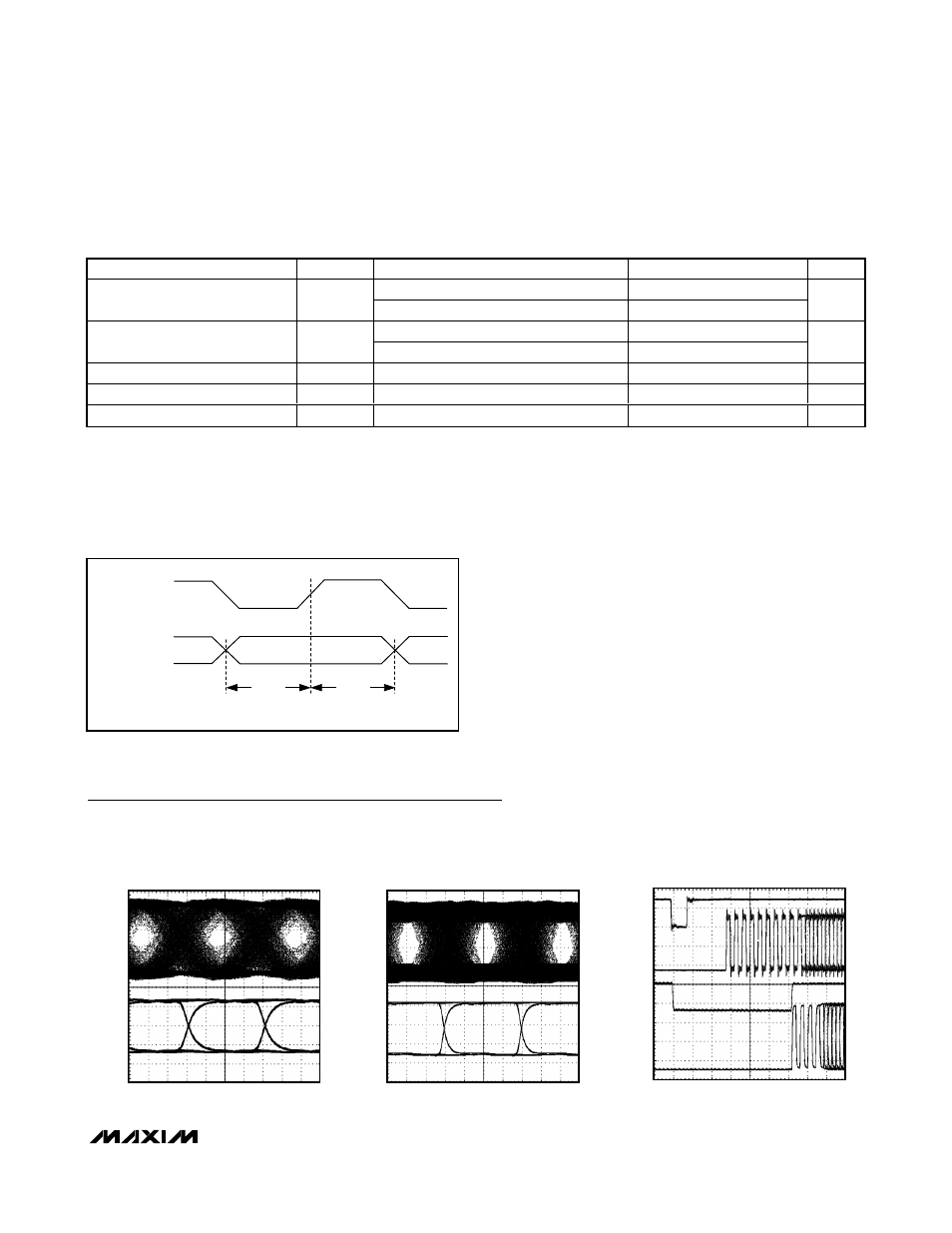

1.244Gbps

INPUT AND OUTPUT EYE DIAGRAMS

MAX3634 toc01

200ps/div

SDI

SDO

622Mbps

INPUT AND OUTPUT EYE DIAGRAMS

MAX3634 toc02

400ps/div

SDI

SDO

BURST CAPTURE AT 1.244Gbps

MAX3634 toc03

1ns/div

RST

SDI

SDO

LOCK

(SCLK+) - (SCLK-)

(SDO+) - (SDO-)

t

CLK-Q

t

Q-CLK

Figure 1. Definition of Clock-to-Q and Q-to-Clock Delay