Deep power-down – Rainbow Electronics AT45DB021E User Manual

Page 29

29

AT45DB021E [PRELIMINARY DATASHEET]

8789B–DFLASH–11/2012

10.

Deep Power-Down

During normal operation, the device will be placed in the standby mode to consume less power as long as the CS pin

remains deasserted and no internal operation is in progress. The Deep Power-Down command offers the ability to place

the device into an even lower power consumption state called the Deep Power-Down mode.

When the device is in the Deep Power-Down mode, all commands including the Status Register Read command will be

ignored with the exception of the Resume from Deep Power-Down command. Since all commands will be ignored, the

mode can be used as an extra protection mechanism against program and erase operations.

Entering the Deep Power-Down mode is accomplished by simply asserting the CS pin, clocking in the opcode B9h, and

then deasserting the CS pin. Any additional data clocked into the device after the opcode will be ignored. When the CS

pin is deasserted, the device will enter the Deep Power-Down mode within the maximum time of t

EDPD

.

The complete opcode must be clocked in before the CS pin is deasserted; otherwise, the device will abort the operation

and return to the standby mode once the CS pin is deasserted. In addition, the device will default to the standby mode

after a power cycle.

The Deep Power-Down command will be ignored if an internally self-timed operation such as a program or erase cycle is

in progress. The Deep Power-Down command must be reissued after the internally self-timed operation has been

completed in order for the device to enter the Deep Power-Down mode.

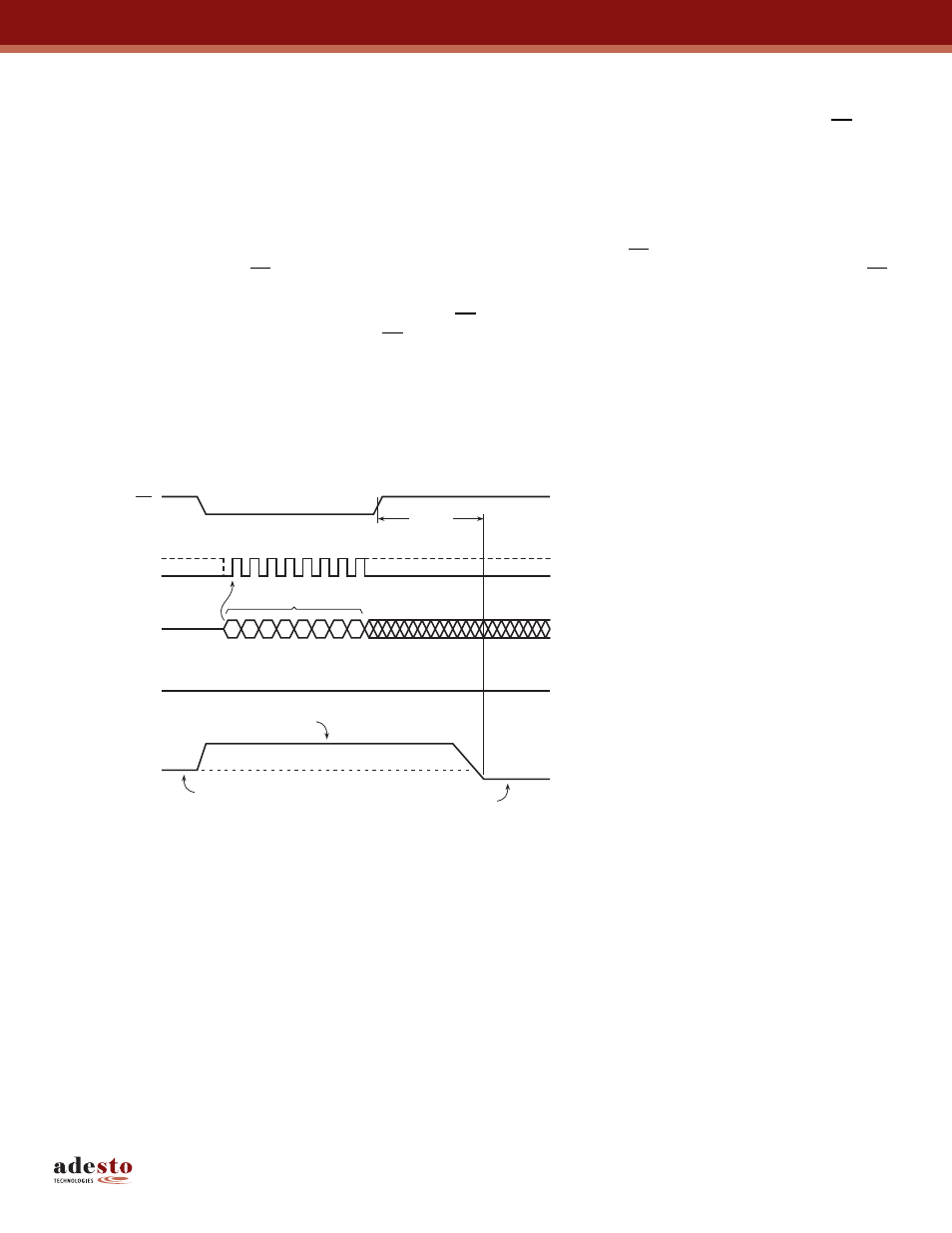

Figure 10-1. Deep Power-Down

SCK

CS

SI

SO

MSB

I

CC

2

3

1

0

1

0

1

1

1

0

0

1

6

7

5

4

Opcode

High-impedance

Standby Mode Current

Active Current

Deep Power-Down Mode Current

t

EDPD