Eeprom read/write access, Eeprom address register – eearh and eearl, Eeprom data register – eedr – Rainbow Electronics AT90C8534 User Manual

Page 28: Eeprom control register – eecr

AT90C8534

28

EEPROM Read/Write Access

The EEPROM access registers are accessible in the I/O space.

The write access time is in the range of 2.5 - 35 ms, depending on the V

CC

voltages. A self-timing function lets the user soft-

ware detect when the next byte can be written. A special EEPROM Ready interrupt can be set to trigger when the

EEPROM is ready to accept new data.

In order to prevent unintentional EEPROM writes, a specific write procedure must be followed. Refer to the description of

the EEPROM Control Register for details on this.

When the EEPROM is written, the CPU is halted for two clock cycles before the next instruction is executed. When the

EEPROM is read, the CPU is halted for four clock cycles before the next instruction is executed.

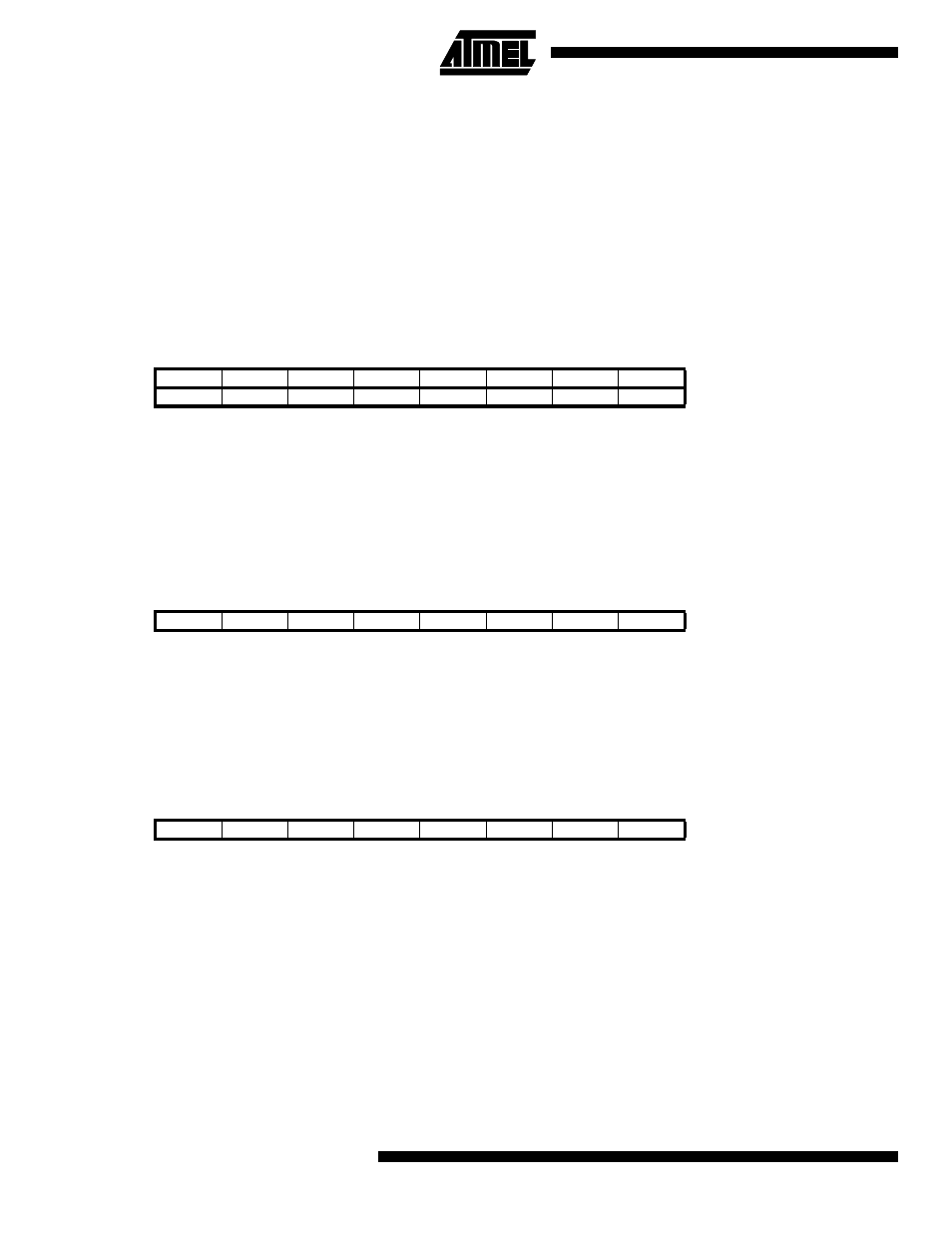

EEPROM Address Register – EEARH and EEARL

The EEPROM Address Registers (EEARH and EEARL) specify the EEPROM address in the 512 bytes EEPROM space.

The EEPROM data bytes are addressed linearly between 0 and 511.

EEPROM Data Register – EEDR

•

Bits 7..0 – EEDR7.0: EEPROM Data

For the EEPROM write operation, the EEDR register contains the data to be written to the EEPROM in the address given

by the EEAR register. For the EEPROM read operation, the EEDR contains the data read out from the EEPROM at the

address given by EEAR.

EEPROM Control Register – EECR

•

Bits 7..4 – Res: Reserved Bits

These bits are reserved bits in the AT90S8535 and will always read as zero.

•

Bit 3 – EERIE: EEPROM Ready Interrupt Enable

When the I bit in SREG and EERIE are set (one), the EEPROM Ready Interrupt is enabled. When cleared (zero), the

interrupt is disabled. The EEPROM Ready interrupt generates a constant interrupt when EEWE is cleared (zero).

•

Bit 2 – EEMWE: EEPROM Master Write Enable

The EEMWE bit determines whether setting EEWE to one causes the EEPROM to be written. When EEMWE is set (one),

setting EEWE will write data to the EEPROM at the selected address. If EEMWE is zero, setting EEWE will have no effect.

When EEMWE has been set (one) by software, hardware clears the bit to zero after four clock cycles. See the description

of the EEWE bit for a EEPROM write procedure.

Bit

15

14

13

12

11

10

9

8

$1F ($3F)

–

–

–

–

–

–

–

EEAR9

EEARH

$1E ($3E)

EEAR7

EEAR6

EEAR5

EEAR4

EEAR3

EEAR2

EEAR1

EEAR0

EEARL

7

6

5

4

3

2

1

0

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial value

0

0

0

0

0

0

0

x

x

x

x

x

x

x

x

x

Bit

7

6

5

4

3

2

1

0

$1D ($3D)

MSB

LSB

EEDR

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial value

0

0

0

0

0

0

0

0

Bit

7

6

5

4

3

2

1

0

$1C ($3C)

–

–

–

–

EERIE

EEMWE

EEWE

EERE

EECR

Read/Write

R

R

R

R

R/W

R/W

R/W

R/W

Initial value

0

0

0

0

0

0

0

0