Interrupt handling, Figure 24, Figure 25 – Rainbow Electronics AT90C8534 User Manual

Page 20

AT90C8534

20

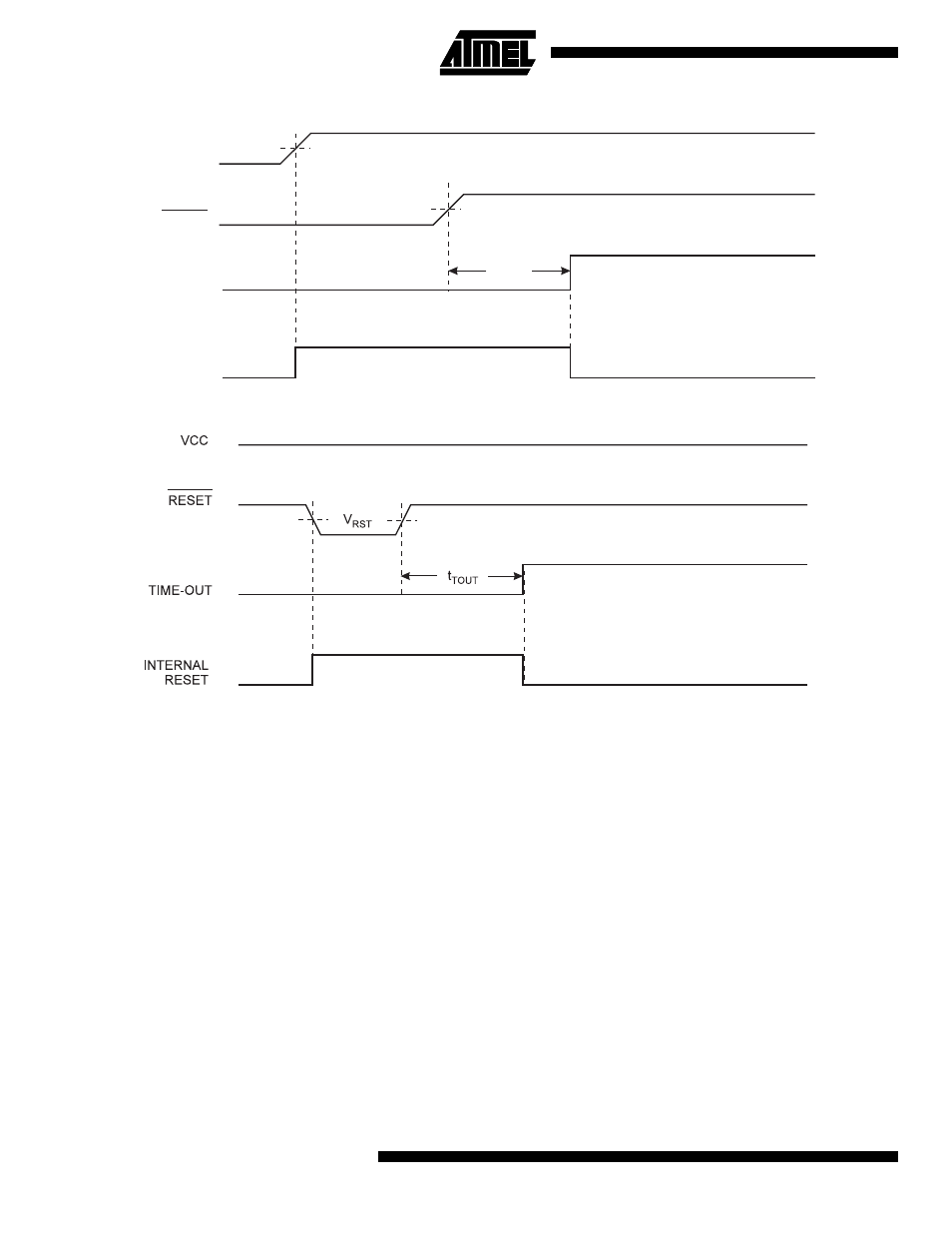

Figure 24. External Reset on Start-up

Figure 25. External Reset during Operation

Interrupt Handling

The AT90C8534 has two 8-bit Interrupt Mask control registers; GIMSK (General Interrupt Mask register) and TIMSK

(Timer/Counter Interrupt Mask register).

When an interrupt occurs, the Global Interrupt Enable I-bit is cleared (zero) and all interrupts are disabled. The user soft-

ware can set (one) the I-bit to enable nested interrupts. The I-bit is set (one) when a Return from Interrupt instruction (RETI)

is executed.

When the Program Counter is vectored to the actual interrupt vector in order to execute the interrupt handling routine, hard-

ware clears the corresponding flag that generated the interrupt. Some of the interrupt flags can also be cleared by writing a

logical “1” to the flag bit position(s) to be cleared.

If an interrupt condition occurs when the corresponding interrupt enable bit is cleared (zero), the interrupt flag will be set

and remembered until the interrupt is enabled or the flag is cleared by software.

If one or more interrupt conditions occur when the global interrupt enable bit is cleared (zero), the corresponding interrupt

flag(s) will be set and remembered until the global interrupt enable bit is set (one), and will be executed by order of priority.

Note that the status register is not automatically stored when entering an interrupt routine and restored when returning from

an interrupt routine. This must be handled by software.

VCC

RESET

TIME-OUT

INTERNAL

RESET

t

TOUT

V

POT

V

RST