Specifications, Differential data ready output, Built-in self test (bist) – Rainbow Electronics TS81102G0 User Manual

Page 9: Absolute maximum ratings

9

TS81102G0

2105C–BDC–11/03

Differential Data

Ready Output

The front edge of the DataReady output occurs when data is available on the corresponding

port. The frequency of this clock depends on the conversion ratio (1:8 or 1:4), with a duty cycle

of 50%.

The definition is the same as for single-ended output data, but the buffers are differential.

This corresponds to the “Adjustable Logic Differential” in the pinout description.

Built-in Self Test

(BIST)

A pseudo-random 10-bit generator is implemented in the DMUX. It generates a 10-bit signal in

the output of the DMUX, with a period of 512 input clocks. The probability of occurrence of

codes is uniformly spread over the 1024 possible codes: 0 or 1/1024.

Note that the 256 codes of bits 1 to 8 occur at least once. They start with a BIST command, in

phase with the FS/8 clock on Port A. The logic output obtained on the A to H ports depends on

the conversion ratio. The driving clock of BIST is Clkln. The ClklnType must be set to ‘1’

(DataReady ADC clock) to have a different 10-bit code on each output.

The complete BIST sequence is available on request.

Specifications

Absolute

Maximum Ratings

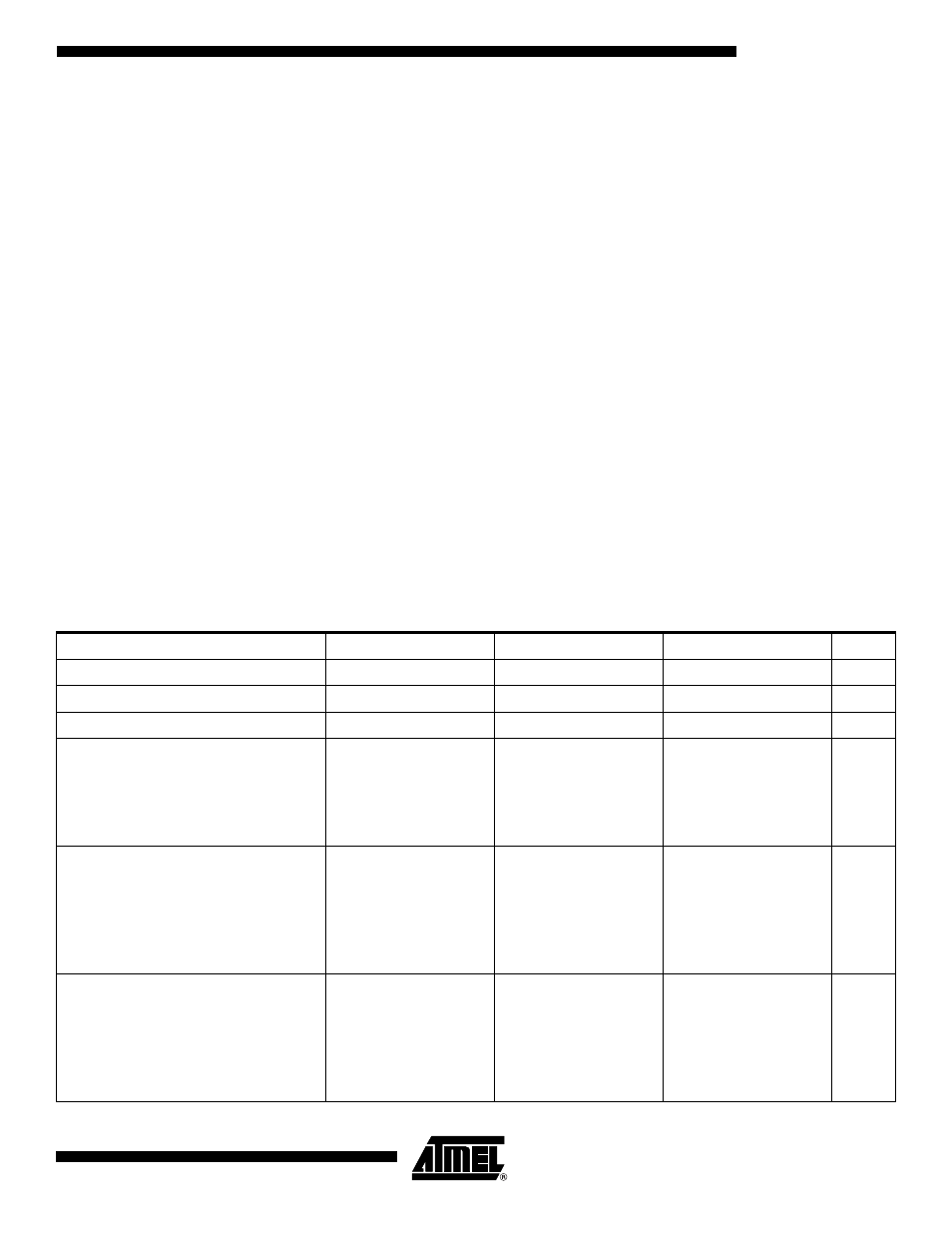

Table 2.

Absolute Maximum Ratings

Parameter

Symbol

Comments

Value

Unit

Positive supply voltage

V

CC

GND to 6

V

Positive output buffer supply voltage

V

PLUSD

GND to 4

V

Negative supply voltage

V

EE

GND to -6

V

Analog input voltages

ADCDelAdjCtrl,

ADCDelAdjCtrlb or

DMUXDelAdjCtrl,

DMUXDelAdjCtrlb or

SwiAdj

Voltage range for each

pad

Differential voltage

range

-1 to +1

-1 to +1

V

ECL 50

Ω

input voltage

Clkln or Clklnb or

I[0…9] or I[0…9]b or

SyncReset or

SyncResetb or

ADCDelAdjln or

ADCDelAdjlnb

Voltage range for each

pad

-2.2 to +0.6

V

Maximum difference between ECL 50

Ω

input voltages

Clkln – Clklnb or

I[0…9] - I[0…9]b or

SyncReset –

Syncresetb or

ADCDelAdjln -

ADCDelAdjlnb

Minimum differential

swing

Maximum differential

swing

0.1

2

V