Block diagram – Rainbow Electronics TS81102G0 User Manual

Page 2

2

TS81102G0

2105C–BDC–11/03

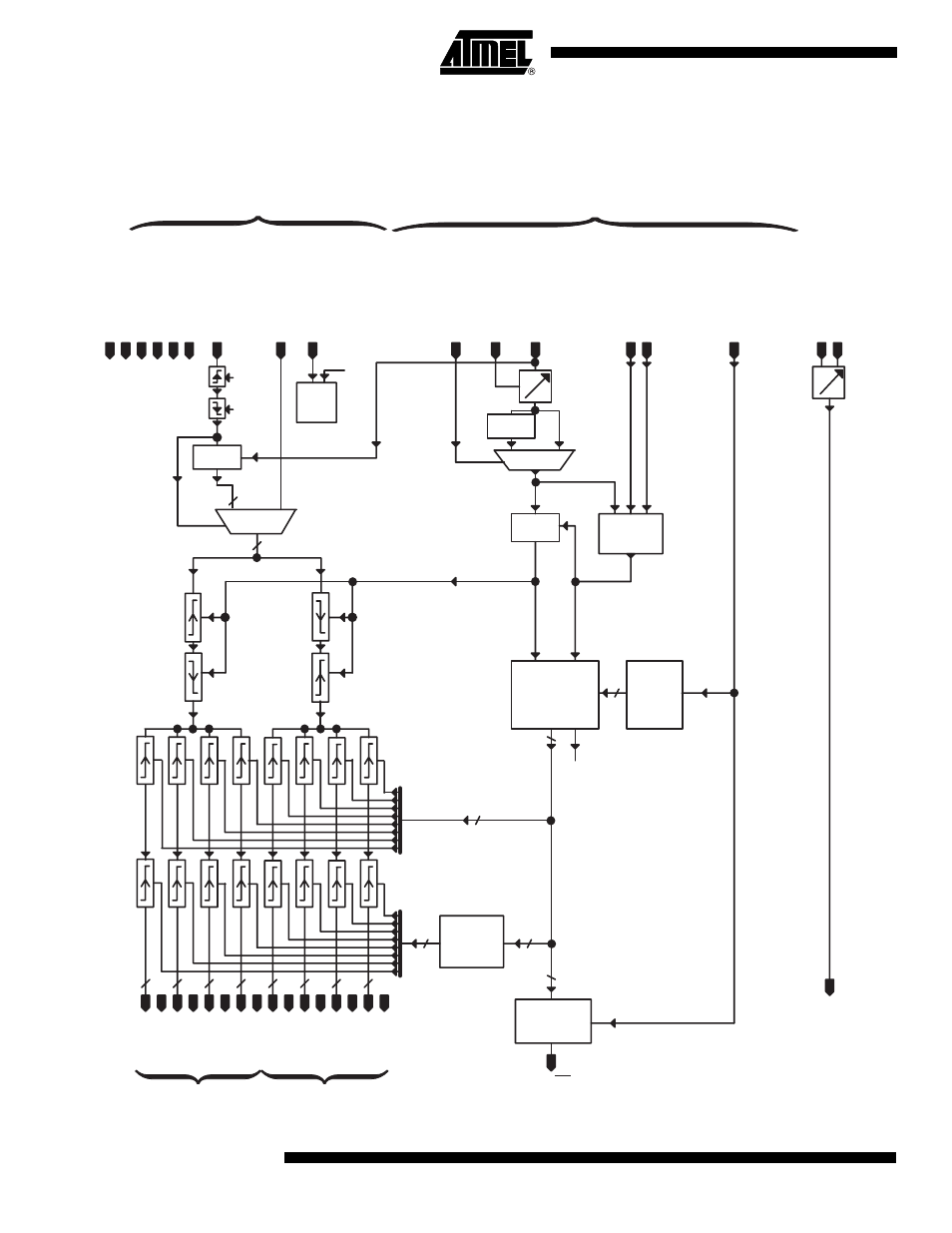

Block Diagram

Figure 1.

Block Diagram

B 2

Counter

(8 stage

shift register)

DataReady

generation

Data Path

Clock Path

mux

Port Selection Clock

Data

Output

Clock

A[0..7/9]

C[0..7/9]

E[0..7/9]

G[0..7/9]

B[0..7/9]

D[0..7/9]

F[0..7/9]

H[0..7/9]

RefA

RefC

RefE

RefG

RefB

RefD

RefF

RefH

Even Ports

Odd Ports

mux

ClkIn

DEMUXDelAdjCtrl

ClkInT

ype

AsyncReset

RatioSel

delay

delay

ADCDelAdjOut

ADCDelAdjCtrl

ADCDelAdjIn

SwiAdj

VplusDOut

VEE

GND

BIST

I[0..7/9]

NbBit

Latch Sel Even/Odd [1..8/10]

even

master

latch

even

slave

latch

odd

master

latch

odd

slave

latch

8/10

8

Counter

NAP

RatioSel

8/10

Status

ClkPar

8

8

3

8

1

VCC

DR/DR

FS/8

FS/8

BIST

8/10

Phase

control

SyncReset

RstGen

Reset

DIODE

(to be confirmed)