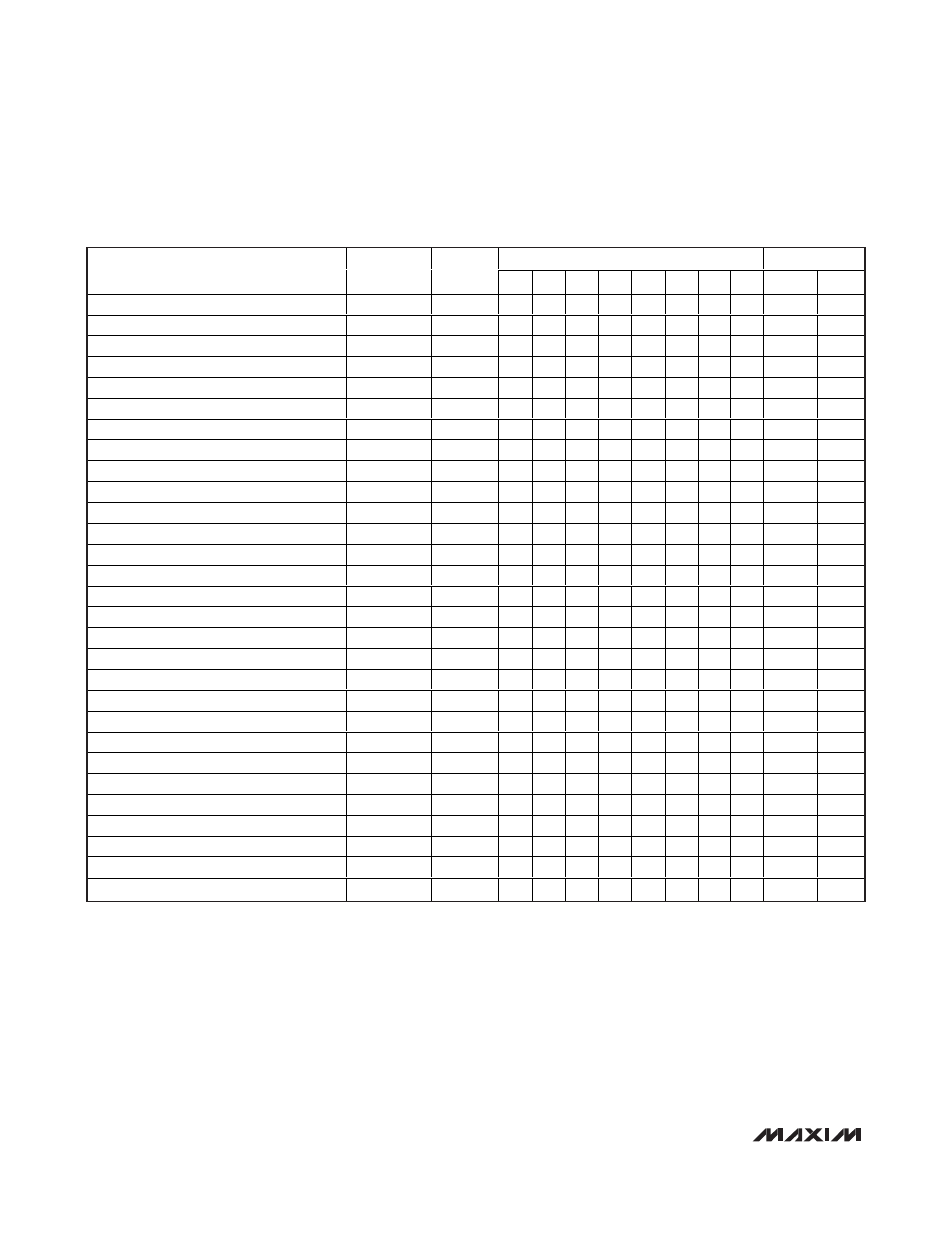

Table 6. register address map – Rainbow Electronics MAX11008 User Manual

Page 46

MAX11008

Dual RF LDMOS Bias Controller with

Nonvolatile Memory

46

______________________________________________________________________________________

COMMAND BITS

HEX CODE

REGISTER

MNEMONIC

SEE

TABLE

C7

C6

C5

C4

C3

C2

C1

C0

WRITE READ

Channel 1 High Temperature Threshold

TH1

7

R

W

0

1

0

0

0

0

0

20

A0

Channel 2 High Temperature Threshold

TH2

7

R

W

0

1

0

1

0

0

0

28

A8

Channel 1 Low Temperature Threshold

TL1

8

R

W

0

1

0

0

0

1

0

22

A2

Channel 2 Low Temperature Threshold

TL2

8

R

W

0

1

0

1

0

1

0

2A

AA

Channel 1 High Current Threshold

IH1

9

R

W

0

1

0

0

1

0

0

24

A4

Channel 1 Low Current Threshold

IL1

9

R

W

0

1

0

0

1

1

0

26

A6

Channel 2 High Temperature Threshold

IH2

10

R

W

0

1

0

1

1

0

0

2C

AC

Channel 2 Low Temperature Threshold

IL2

10

R

W

0

1

0

1

1

1

0

2E

AE

Hardware Configuration

HCFIG

11

R

W

0

1

1

0

0

0

0

30

B0

Alarm Software Configuration

ALMSCFIG

12

R

W

0

1

1

0

0

1

0

32

B2

Software Configuration

SCFIG

13

R

W

0

1

1

0

1

0

0

34

B4

Alarm Hardware Configuration

ALMHCFIG

14

R

W

0

1

1

0

1

1

0

36

B6

VSET1

VSET1

15

R

W

0

1

1

1

0

0

0

38

B8

VSET2

VSET2

15

R

W

0

1

1

1

1

0

0

3C

BC

APC1 Parameter

HIST_APC1

16

R

W

0

1

1

1

0

1

0

3A

BA

APC2 Parameter

HIST_APC2

16

R

W

0

1

1

1

0

1

0

3E

BE

DAC1 Input (Write Only)

IDAC1

17

0

1

0

1

1

0

0

0

58

—

DAC2 Input (Write Only)

IDAC2

17

0

1

0

1

1

1

0

0

5C

—

DAC1 Input and Output (Write Only)

IODAC1

18

0

1

0

1

1

0

1

0

5A

—

DAC2 Input and Output (Write Only)

IODAC2

18

0

1

0

1

1

1

1

0

5E

—

PGA Calibration Control ( Write Only)

PGACAL

19

0

1

1

0

0

0

0

0

60

—

ADC Conversion (Write Only)

ADCCON

20

0

1

1

0

0

0

1

0

62

—

Software Shutdown (Write Only)

SSHUT

21

0

1

1

0

0

1

0

0

64

—

Load DAC (Write Only)

LDAC

22

0

1

1

0

0

1

1

0

66

—

Message (Write Only)

—

23

0

1

1

0

1

1

1

0

6E

—

FIFO

—

24

R

W

1

1

1

0

0

1

0

72

80

Software Clear (Write Only)

SCLR

25

0

1

1

1

0

1

0

0

74

—

LUT Streaming (Write Only)

—

27

0

1

1

1

1

1

1

0

7E

—

Flag (Read Only)

—

26

1

1

1

1

0

1

1

0

—

F6

Table 6. Register Address Map

The following properties of the register address map should be noted:

• All register data is volatile.

• Data stored in locations TH1, TH2, TL1, TL2, IH1, IH2, IL1, IL2, HCFIG, ALMSCFIG, SCFIG, ALMHCFIG, VSET1,

VSET2, IDAC1, IDAC2, IODAC1, IODAC2, PGACAL, ADCCON, SSHUT, and LDAC can be loaded from EEPROM

at power-up or after a full reset.

• Write to the FIFO register only in LUT streaming mode (see the

LUT Streaming Mode

section).