Table 5a. lut pointer sizes and offset ranges, Table 5c. selectable lut sizes, Table 5d. selectable lut starting addresses – Rainbow Electronics MAX11008 User Manual

Page 42

MAX11008

Dual RF LDMOS Bias Controller with

Nonvolatile Memory

42

______________________________________________________________________________________

4) The resulting LUT pointer value is bound-limited to

ensure it fits within the corresponding LUT. Negative

pointer values are limited to zero, and pointer values

that extend beyond the range of the LUT are limited

to the last entry.

5) The final LUT pointer value is calculated by shifting

SOT to the left by 5 bits and then adding it to the

current LUT pointer value. If no linear interpolation

(INT = 00) is to be performed, the resulting LUT

pointer value is equal to the absolute EEPROM

address from which the LUT data is retrieved. If lin-

ear interpolation is to be performed (INT = 01, 10, or

11), the two LUT addresses that are closest to the

resulting LUT pointer value and their corresponding

data values are entered into the following equation

to calculate the interpolated data value that is used

in the V

GATE_

calculation:

where PTR is the calculated LUT pointer value with

fractional bits, ADD1 and ADD2 are the two LUT

addresses closest to the value of PTR, and DATA1 and

DATA2 are the LUT data values stored at ADD1 and

ADD2.

LUT Pointer Example 1 (No Interpolation)

POFF = 001000 (offset of +8).

INT = 00 (no interpolation/LUT pointer does not have

any fractional bits).

PSIZE = 00 (5-bit LUT pointer not including any frac-

tional bits).

TSIZE = 001 (LUT has 32 data locations).

SOT = 010 (LUT starts at EEPROM address 40 hex).

Interpolated Data

DATA

PTR

ADD

ADD

ADD

x DATA

DATA

(

)

=

+

−

−

⎛

⎝

⎜

⎞

⎠

⎟

−

1

1

2

1

2

1

DATA

BITS

BIT

NAME

RESET

STATE

FUNCTION

D [ 15:10] POFF

000000

POFF

bits.

D[9:8]

INT

00

Interpolation degree select bits.

See Table 5b.

D[7:6]

PSIZE

00

LUT pointer size bit. See Table

5a.

D[5:3]

TSIZE

000

LUT size bit. See Table 5c.

D[2:0]

SOT

000

Start of table address bits. See

Table 5d.

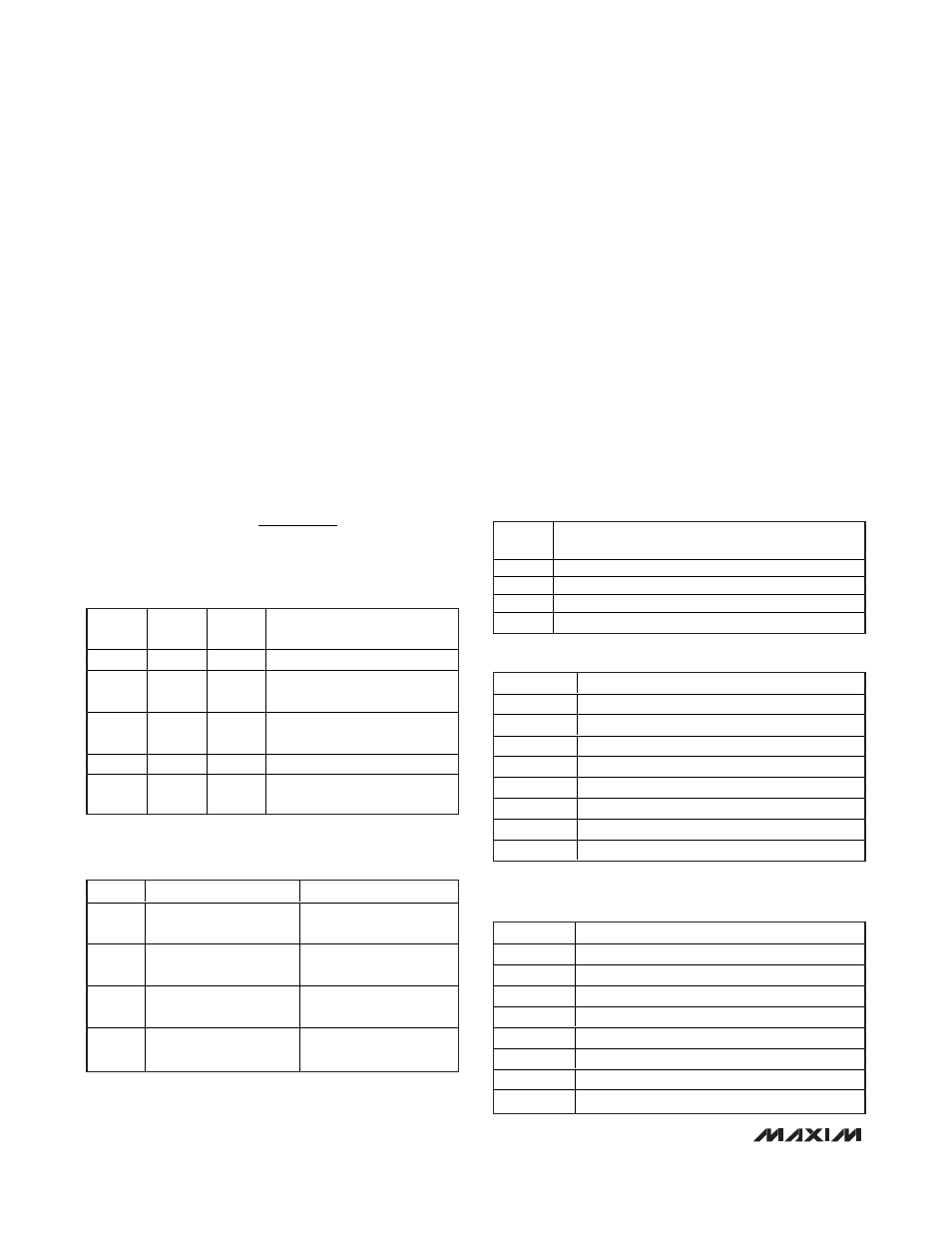

Table 5. Temperature/APC LUT

Configuration Register

PSIZE

LUT POINTER SIZE

POFF OFFSET RANGE*

00

5-bit pointer (access up

to 32 data locations)

-32 to +31

01

6-bit pointer (access up

to 64 data locations)

-32 to +31

10

7-bit pointer (access up

to 128 data locations)

-64 to +62 (in steps of 2)

11

8-bit pointer (access up

to 256 data locations)

- 128 to + 124 ( i n step s of 4)

Table 5a. LUT Pointer Sizes and Offset

Ranges

INT

NUMBER OF FRACTIONAL BITS ADDED TO

LUT POINTER

00

0

01

1

≥ 1:2 interpolation

10

2

≥ 1:4 interpolation

11

3

≥ 1:8 interpolation

Table 5b. Fractional Bits Added to LUT

Pointer for Linear Interpolation

*POFF is either a negative or positive number. When POFF is

negative its value is represented in two’s complement format.

TSIZE

LUT SIZE

000

Unused

001

Table size of 32 data locations

010

Table size of 64 data locations

011

Table size of 96 data locations

100

Table size of 128 data locations

101

Table size of 160 data locations

110

Table size of 192 data locations

111

Unused

Table 5c. Selectable LUT Sizes

SOT

STARTING ADDRESS IN EEPROM (HEX)

000

Unused

001

Unused

010

0x40

011

0x60

100

0x80

101

0xA0

110

0xC0

111

0xE0

Table 5d. Selectable LUT Starting

Addresses