Rainbow Electronics MAX11008 User Manual

Page 28

MAX11008

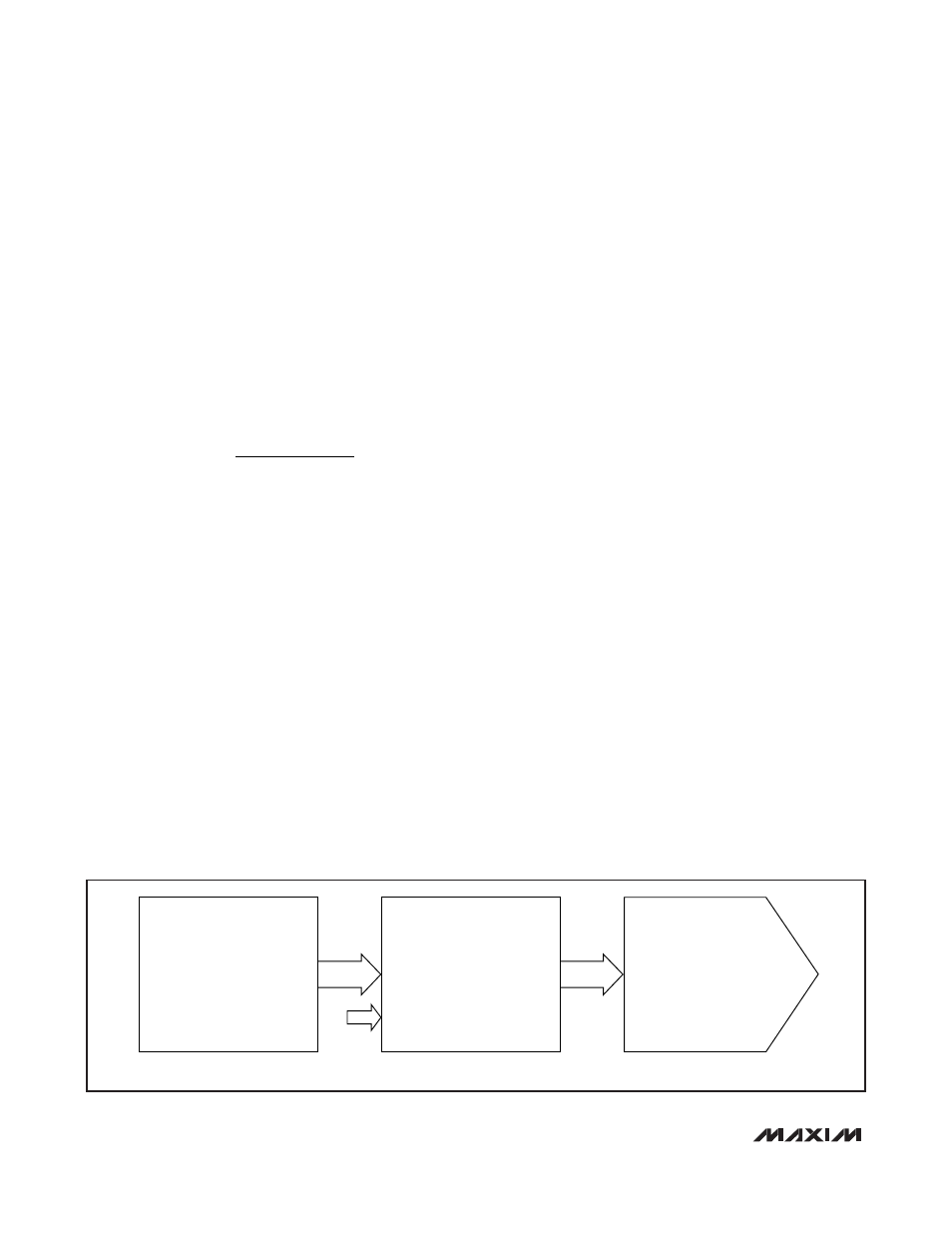

Figure 16 shows the functional diagram of the

MAX11008 DACs. Each DAC includes an input and

output register. The input registers hold the result of the

most recent write operation, and the output registers

hold the current output code for the respective DAC.

Data written to a DAC input register is transferred to its

output register by writing to the Load DAC register (see

Table 22). Alternatively, write data directly to the output

register using the DAC Input and Output Data register.

The analog output voltages of the DACs (before amplifi-

cation by the gate-drive amplifiers) are calculated with

the following equation:

where V

DACREF

is the value of the internal or external

reference voltage and CODE is the decimal value of the

12-bit code contained in the output register.

Gate-Drive Amplifiers

The gate-drive amplifiers are proportional to the analog

outputs of the 12-bit DACs and provide the necessary

gate voltage to drive the external LDMOS transistors.

Both amplifiers have a fixed gain of 2V/V and are capa-

ble of sourcing or sinking up to 2mA of current. Output

short-circuit protection prevents output currents from

exceeding ±25mA.

The gate output is equal to the DAC output voltage

amplified by 2.

V

GATE_

= 2 x V

DAC

See the

Software Configuration Registers

and

Temperature/APC LUT Configuration Registers

sections

for information on how the gate voltages are controlled

by temperature and APC samples.

Output Clamp

The MAX11008 features an output clamp mode that

protects the external LDMOS transistors by connecting

the gate-drive amplifier outputs (GATE_) to AGND. The

clamp mode can be controlled by the OPSAFE_ digital

inputs or by setting the appropriate ALMCLMP[1:0] bits

in the Alarm Hardware Configuration register (see

Table 14). When using the OPSAFE_ digital inputs, pull

OPSAFE_ high to enter clamp mode and pull OPSAFE_

low to exit clamp mode. The clamp can also be activat-

ed automatically from the alarm trip point setting regis-

ters; see the

Alarm Software Configuration Register

(ALMSCFIG) (Read/Write)

section.

Self-Calibration

Calibrate channel 1 and channel 2 by writing to the

PGA Calibration Control register. The MAX11008 func-

tions after power-up without a calibration. Command a

calibration after powering up the device by setting the

TRACK bit to 0 and the DOCAL bit to 1 (see Table 19).

Subsequently, set the TRACK, DOCAL, and SELFTIME

bits to 1 to enable automatic self-calibration (approxi-

mately every 13ms). This minimizes loss of perfor-

mance over temperature and supply-voltage variation.

Alternatively, run self-calibration manually to control the

timing of the operation. Set the TRACK and DOCAL bits

to 1 and the SELFTIME bit to 0 to perform manually trig-

gered self-calibration.

The self-calibration algorithm cancels offsets at the

PGA-drive amplifier inputs in approximately 50µV incre-

ments to improve accuracy. The self-calibration routine

can be commanded when the DACs are powered

down, but the results will not be accurate. For best

results, run the calibration after the DAC power-up time,

t

DPUEXT

. The ADC’s operation is suspended during a

self-calibration. The BUSY output returning low indi-

cates the end of the self-calibration routine. Wait until

the end of the self-calibration routine before requesting

an ADC conversion.

V

V

CODE

DAC

DACREF

=

×

4096

Dual RF LDMOS Bias Controller with

Nonvolatile Memory

28

______________________________________________________________________________________

Channel 1/Channel 2

CHANNEL 1/

CHANNEL 2 DAC

CHANNEL 1/CHANNEL 2

DAC OUTPUT REGISTERS

CHANNEL 1/CHANNEL 2

DAC INPUT REGISTERS

LDDACCH_

SET TO 1 IN

LOAD DAC

REGISTER

Figure 16. DAC Functional Diagram